この記事でわかること

・シャントレギュレータの動作原理

・シリーズレギュレータICの種類と使い方

・TL431を使った回路設計方法

シャントレギュレータは基準電圧を生成したり、電源回路の電圧制御に利用されます。

一定電圧を維持するツェナーダイオードのような働きをするため回路記号が似ていますが、

内部はオペアンプが内蔵された複雑な回路構成となっており、高い電圧精度を持っています。

本記事ではシャントレギュレータの定番ICであるTL431の使い方と、

回路設計方法について解説します。

<注意>

本記事で紹介する抵抗値等の回路定数については、データーシート等から引用したものであり、

ICの選定も含め、動作を保証するものでは無いため、参考程度として下さい。

シャントレギュレータの動作原理

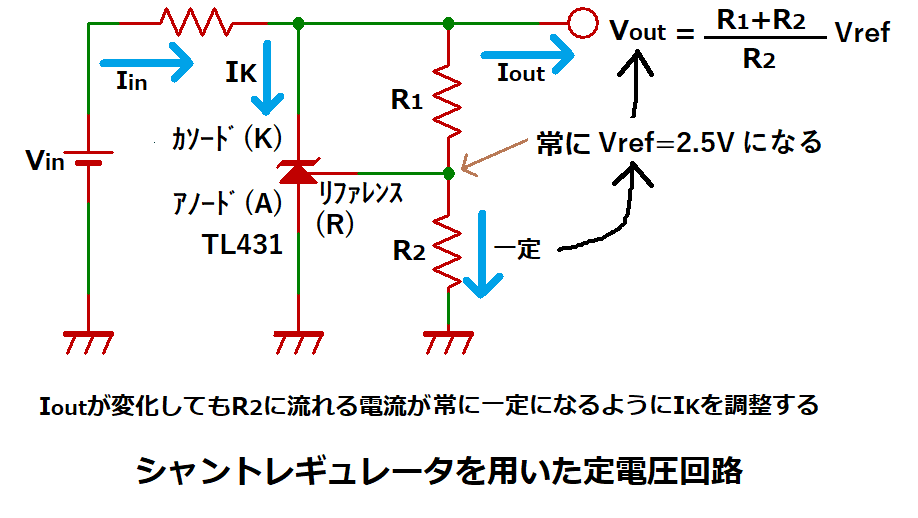

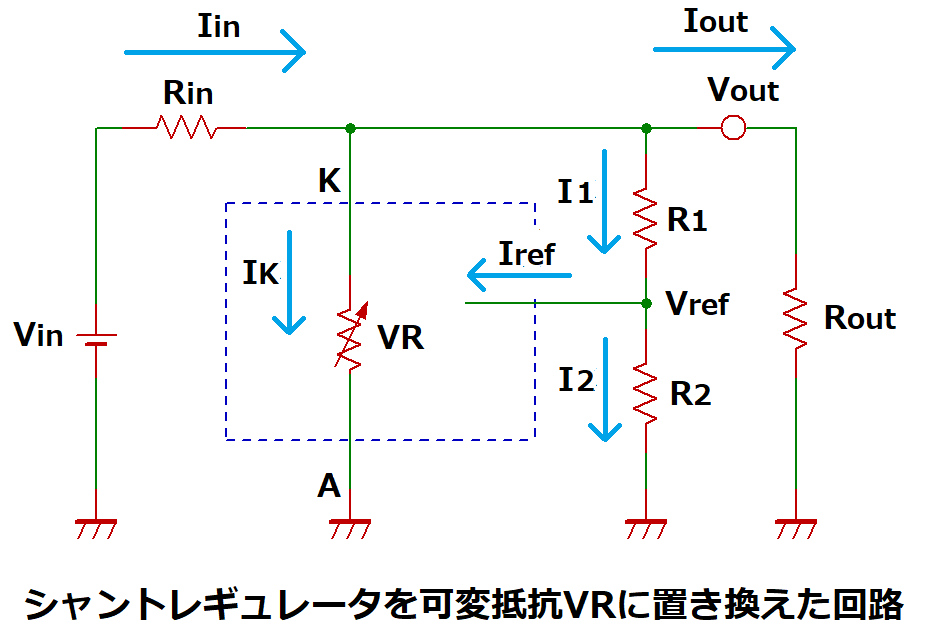

シャントレギュレータのシャント(Shunt)とは「分流」を意味しており、

入力電圧や負荷電流が変動しても、それによる電流変化分をシャントレギュレータに分流させ、

基準電圧を決める抵抗に流れる電流を変化させないことで、出力電圧を一定に保ちます。

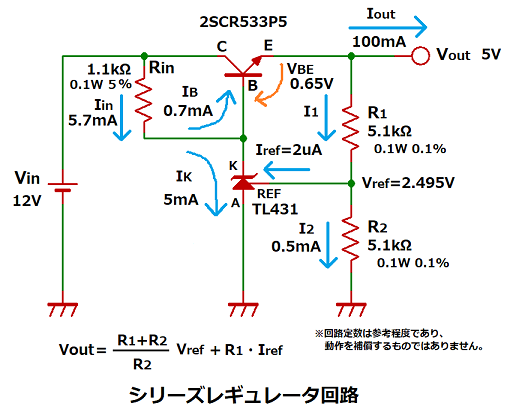

具体的には上図において、VinやIoutが変動しても、リファレンス電圧を2.5Vに維持するため、

R2に流れる電流が変化しないようにシャントレギュレータは電流IKを調整します。

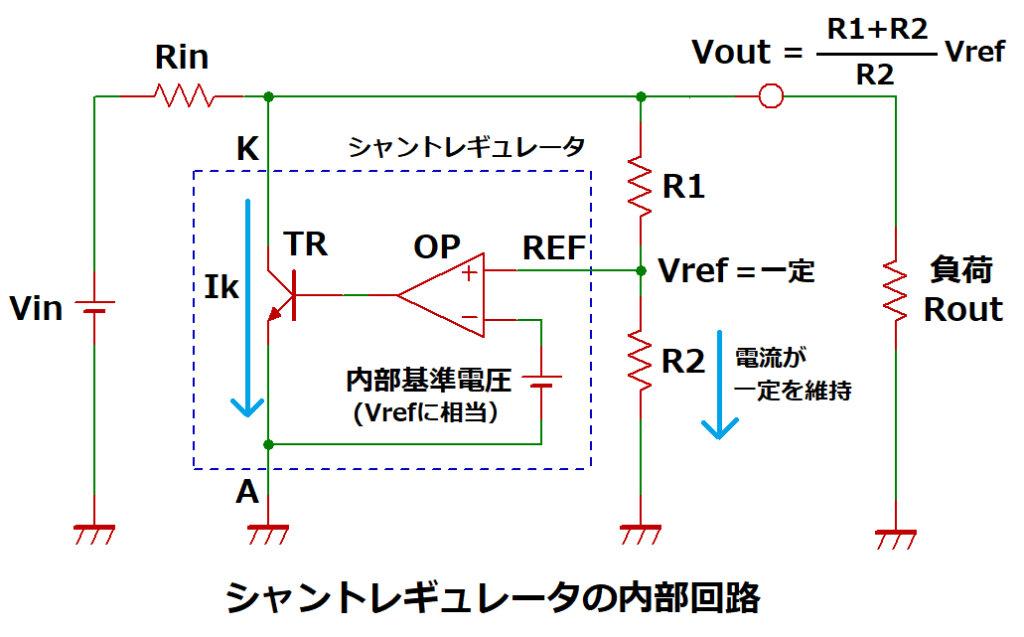

シャントレギュレータがIKを調整する方法を説明します。

シャントレギュレータの内部はオペアンプOPとトランジスタTRから構成されています。

このオペアンプは誤差アンプや、エラーアンプと呼ばれるもので、

±入力の電圧差を検出し、+の方が高い程、OPの出力電圧が高くなります。

OPの+端子はREF端子、-端子は内部基準電圧Vrefに接続され、

その出力はTRのベースに接続されることで、REF端子電圧がVrefより高くなるほど、

流すことができる(※)カソード電流IKが増加します。

※その電流値まで流すことが可能という意味であり、実際に流れる電流はRinによって決まります。

以上の構成で、REF端子電圧がVrefより高いとIKを増やし、低いとIKを減らす動作を行います。

このIKを調整することで、REF端子電圧をVrefに保つことができる原理ですが、

シャントレギュレータを可変抵抗VRに置き換えてみると理解しやすいです。

REF端子電圧=Vrefで一定状態の場合、I2=Vref/R2なので、I2も一定です。

REF端子に流れる電流IrefはTL431のデータシートより4uAと非常に小さいため無視すると、

I1≒I2になるので、I1も一定になります。

ここで、回路に流れる各電流の関係は以下になります。

Iin=IK+I1+Iout=IK+I2+Iout ①

入力電流Iinは次の式でも表現できます。

Iin=(VinーVout)/Rin ②

例えば、入力電圧Vinが上昇した場合、Voutが上昇しないようにするには、

②式よりIinを増やす必要があります。

Voutが一定なら、Iout=Vout/Routにより、Ioutも一定なので、

①式よりIinを増やすにはIKを増やすしかないことから、VRを小さくします。

これは、シャントレギュレータにおいて、Vrefが上昇したらIKを増やす動作に相当します。

次に負荷Routが減少した場合は、Voutが低下しないようにIoutを増やす必要がありますが、

②式よりVinが一定ならIinも一定であり、I2も変化しないことから、

①式よりIoutが増えた分、IKを減らすためにVRを大きくします。

これは、シャントレギュレータにおいて、Vrefが低下したらIKを減らす動作に相当します。

まとめると、VinやRoutの変化によって、IinやIoutが増減しても、

その電流変化分をシャントレギュレータが吸収(IKが増減)することで、

I2が変化しないため、REF端子電圧をVrefに維持できます。

シャントレギュレータの特徴

シャントレギュレータの特徴について、回路記号が似ているツェナーダイオードや、

同じリニアレギュレータ(※)である三端子レギュレーターとの相違点から説明します。

※リニアレギュレータ :入力-出力電圧特性が直線的(リニア)な電源回路

リニアレギュレータについては下記記事で解説しています。

・出力電圧精度が高い

ツェナーダイオードもツェナー電圧Vzで一定電圧を維持できますが、

Vzはツェナーダイオードに流れるツェナー電流Izや、周囲温度による変動が大きく、

電圧精度はあまり高くありません。

ツェナーダイオードについては下記記事で解説しています。

シャントレギュレータの基準電圧Vrefは、カソード電流IKによる変動は殆どなく、

温度による影響も小さいことから、電圧精度はTL431の標準グレードでも2%、

高精度のBグレードなら0.5%と非常に高いです。

・任意の電圧を出力可能

ツェナーダイオードは各種ツェナー電圧Vzがラインナップされていますが、

データシートを見ると、VzはMIN~MAX値の範囲で±2%以上のバラツキがあります。

また、先述したツェナー電流や温度による影響はVzの値によって大きく変わり、

Vzが5~6V以外のものは変動が大きく、基準電圧としては使用するには不向きです。

シャントレギュレータのVrefは種類が少なく、バラツキも存在しますが、

外部抵抗(上図のR1、R2)を調整することで任意の電圧を設定できます。

(TL431の場合、2.5V(Vref)~36Vまでの範囲で設定可能)

・安価で入手性が良い

秋月電子での価格を見ると数十円程度と安く、

TL431と互換性のある他メーカ品も多数存在するため、入手性も良いです。

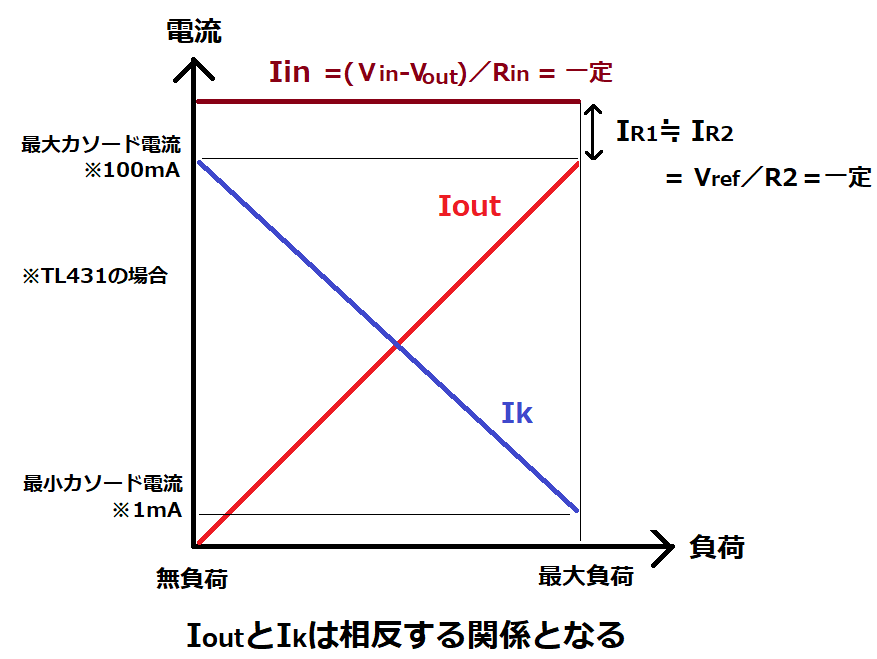

・効率が悪い

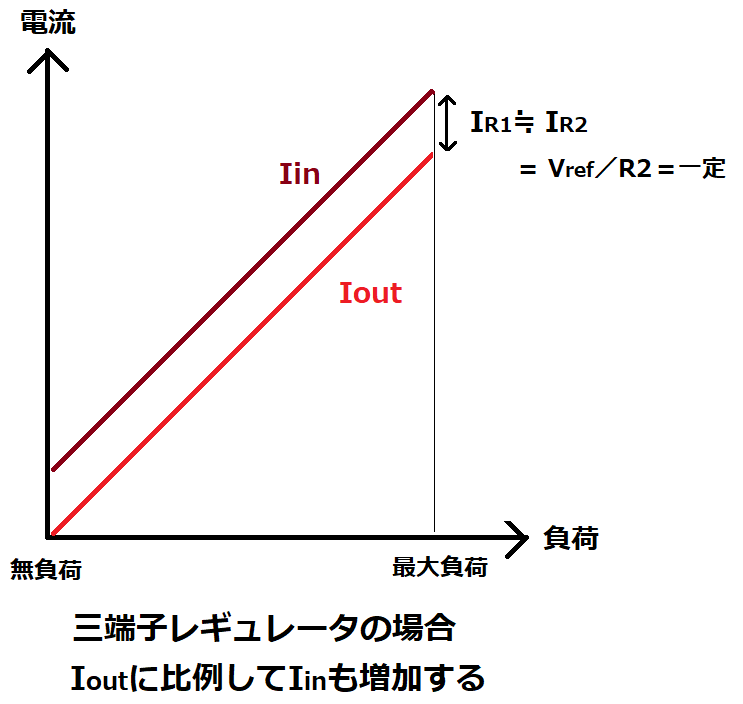

下図は、先程のシャントレギュレータの基本回路について、

Vinが一定で、負荷電流Ioutが変化した時の各電流の関係を示したものです。

これを見ると、Ioutの大きさに関係なく、入力電流Iinは一定であることから、

無負荷時の消費電力(Vin × Iin)は最大負荷時と同じです。

一方、シャントレギュレータと同様に定電圧出力を行う三端子レギュレータ(※)は、

Ioutの大きさに比例してIinが増加するため、負荷が小さければ消費電力も小さくなります。

※:シリーズレギュレータやドロッパとも呼ばれ、入力~出力間に直列(シリーズ)に電圧制御部品がある電源回路

以上のことから、負荷に関係なく消費電力が同じシャントレギュレータは効率が悪いため、

最大負荷時の出力電流が大きい電源回路には不向きです。

シャントレギュレータTL431の種類

TL431のオリジナルはTI(テキサス・インスツルメンツ)製ですが、

Amazonを見ると、コピー品と思われる製品が沢山出てきます。

また、他の型名でもセカンドソース品が数多くあります。

NJM431(日清紡マイクロデバイス(旧:新日本無線))

LM431(元々はナショナル・セミコンダクタだったがTIに吸収)

MN1431(ミネベア ミツミ)

μPC1093(ルネサス・エレクトロニクス)

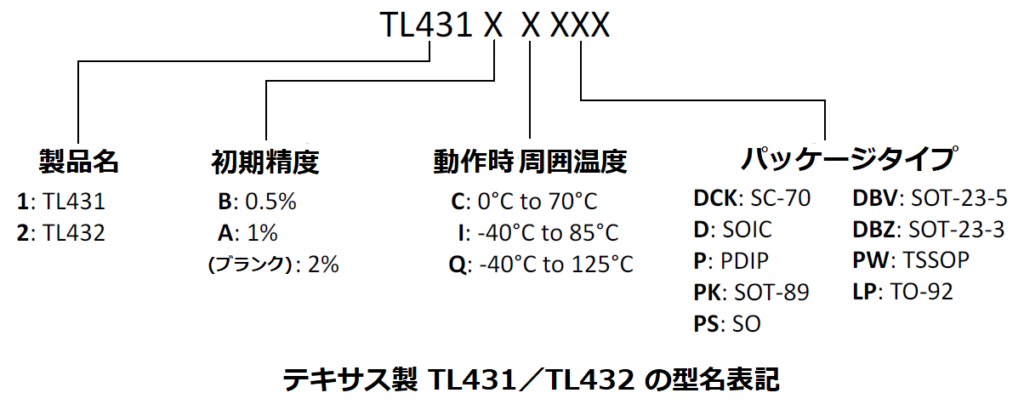

TI製TL431には電圧精度やパッケージタイプにより複数の種類があり、

型名表記は以下のようになっています。

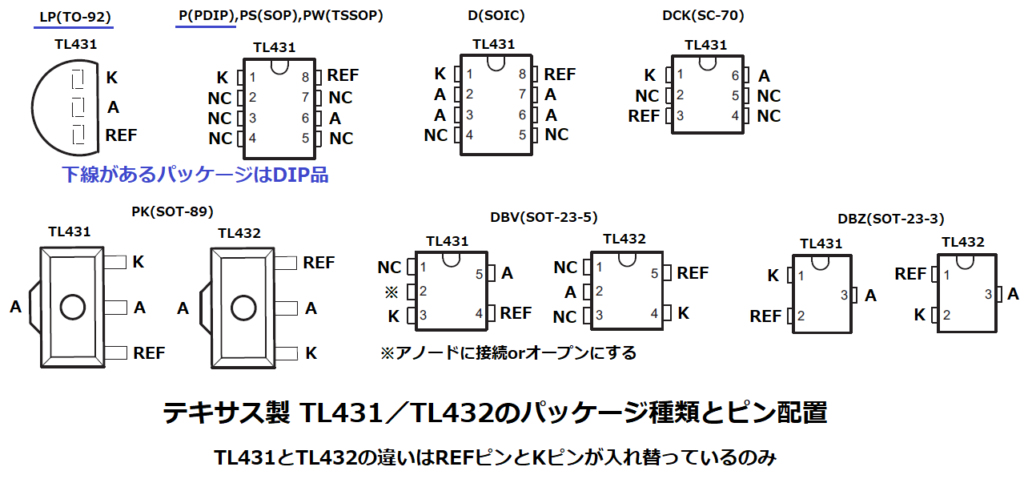

ここで、TL432が出てきますが、TL431との違いはピン配置のみで、

面実装(SMD)タイプのREFとKピンが入れ替っています。

(TL432にはリード部品(DIP)タイプは無し)

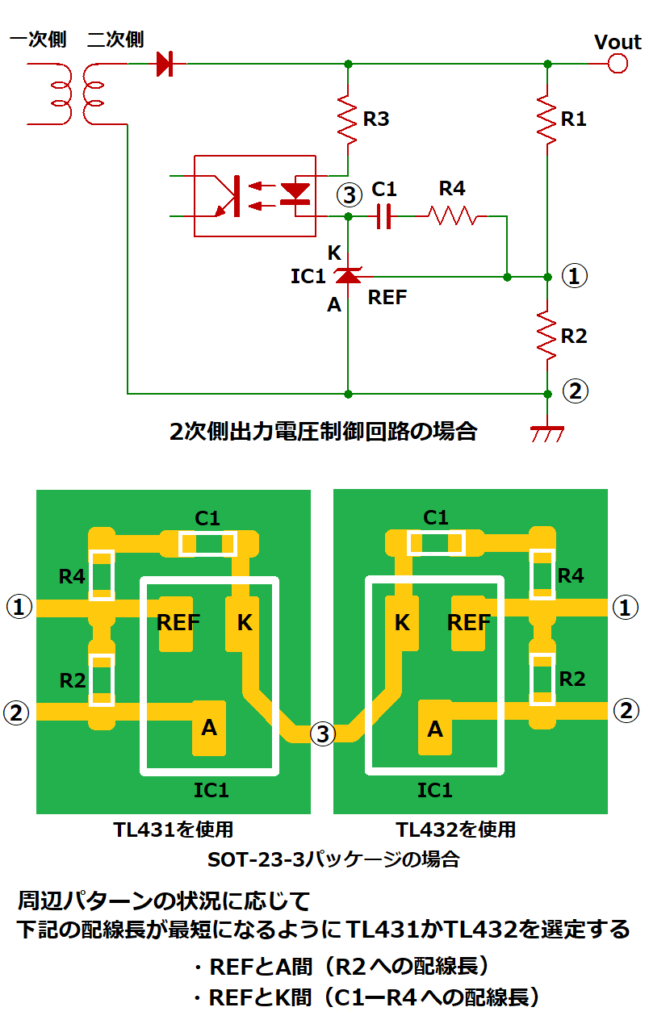

ピン配置違いのデバイスが用意されている理由ですが、

REFピンからのパターンが長いと電圧精度に影響がでるため、

周辺回路パターンの配線状態に応じて、REFパターンを最短にできるデバイスを選択します。

※この回路例(二次側出力電圧制御回路)については後で説明します。

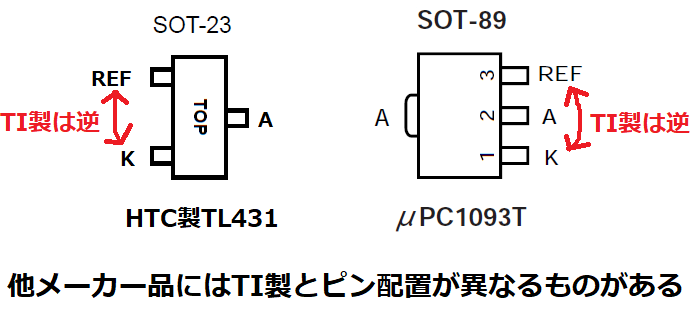

他メーカーの面実装部品でもREFとKピンが入れ替っているものが存在し、

型名が同じ***431でも、ピン配置が異なるものがあるため、

部品変更で配線が変わってしまう場合があるので注意が必要です。

電圧精度については、3つのグレードがあります。(値は周囲温度25℃時)

Bグレード(TL431B): 0.5%

Aグレード(TL431A): 1%

標準グレード(TL431): 2%

基準電圧Vrefについては、TL431は2.495Vですが、このVrefが出力可能な最低電圧になるので、

低電圧回路向けにVref=1.25VのTLV431があり、3.3V以下の電圧出力に利用されています。

TLV431は、シャントレギュレータの動作に必要な最小カソード電流IK(min)も

TL431の1mAに対し、100uAと低消費電力です。

この低電圧タイプについても、各メーカ品があります。

NJM2376(日清紡マイクロデバイス) Vref=1.25V

LMV431(TI:旧ナショセミ)Vref=1.24V

MN1530(ミネベア ミツミ)Vref=1.24/1.25/1.27V

μPC1943/1944(ルネサス・エレクトロニクス)Vref=1.26V

また、高精度で最小カソード電流が60uAの高性能版もあります。

LM4041/4051(TI:旧ナショセミ) Vref=1.225V±0.1%

※上記品はREF端子の無い出力電圧が1.2V固定の2端子タイプもあります。

MN2823(ミネベア ミツミ) Vref=1.136V±0.4%

シャントレギュレータの使い方

TL431を使った基本的な回路について説明します。

基準電圧回路

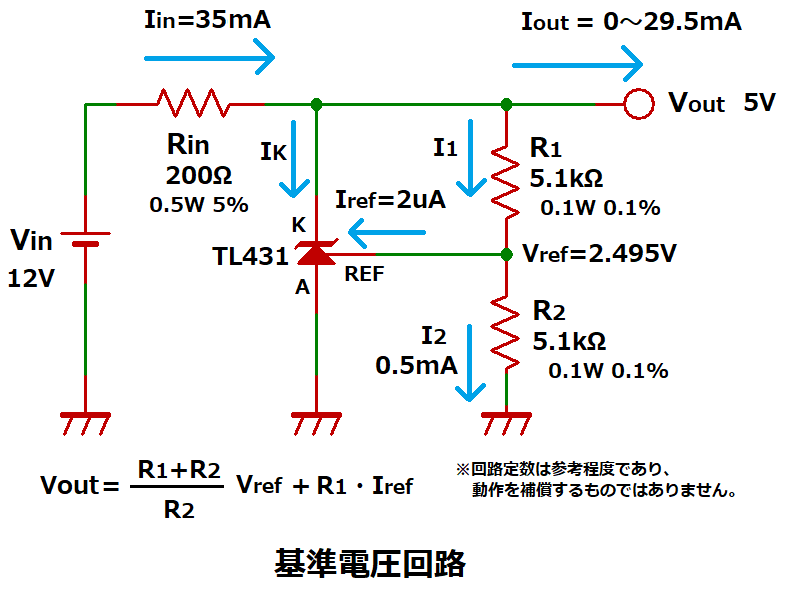

基準電圧源として利用するもので、シャントレギュレータを使った最も基本的な回路です。

先程の動作原理の説明では、REF端子への入力電流Irefが小さいので無視しましたが、

Irefを考慮した場合の出力電圧は以下になります。

Vout=Vref × (R1+R2)/R2+Iref × R1 ③

<③式になる理由>

R2に流れる電流I2は

I2=Vref/R2

R1に流れる電流I1はI2とIrefの合計となるので、R1間電圧VR1は次式になります。

VR1=R1×I1=R1×(I2+Iref)

=R1×(Vref/R2+Iref)

=Vref ×(R1+R2)/R2+Iref×R1

となり、③式になります。

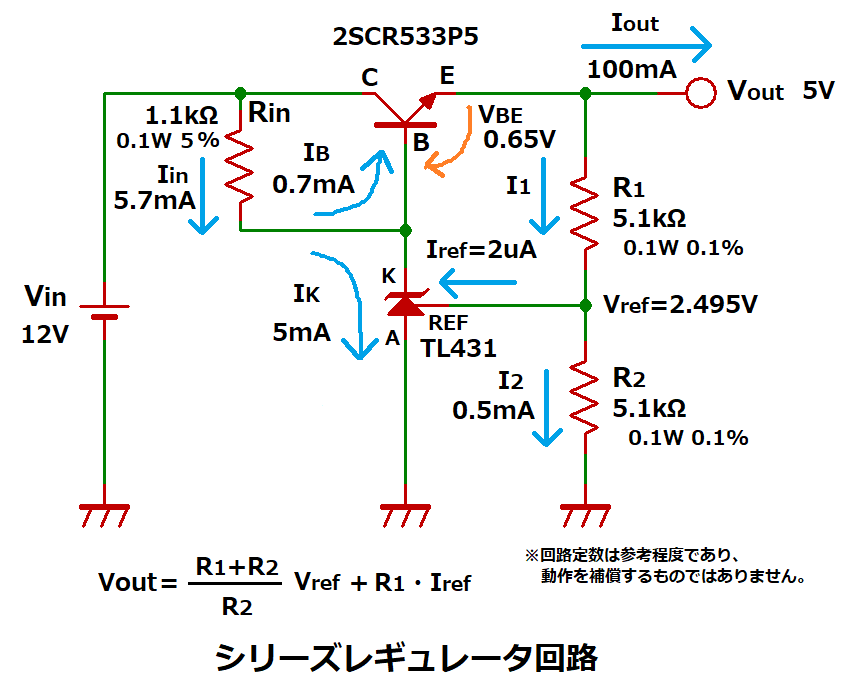

この回路は、入力電圧Vin=12V、出力電圧Vout=5Vにした場合です。

③式において、TL431データシートより、VrefとIrefの平均値(2.495Vと2uA)を代入し、

R1=R2とすると、

Vout=2.495V×2+2uA×R1

R1を5.1kΩとすると、

Vout=4.99V+0.0102V=5.0002V

となり、ほぼ5Vの値が得られます。

次にRinを決めると、②式よりIinが決まります。

①式より、IinはIK、I2、Ioutの合計になりますが、先程説明したようにIinとI2は一定値で、

IoutとIKは相反する関係であることから、無負荷(Iout=0)時にIKが最大となります。

IKの最大値IK(max)はシャントレギュレータの許容損失PD(消費電力の上限)で決まります。

PD=VKA × IK(max)

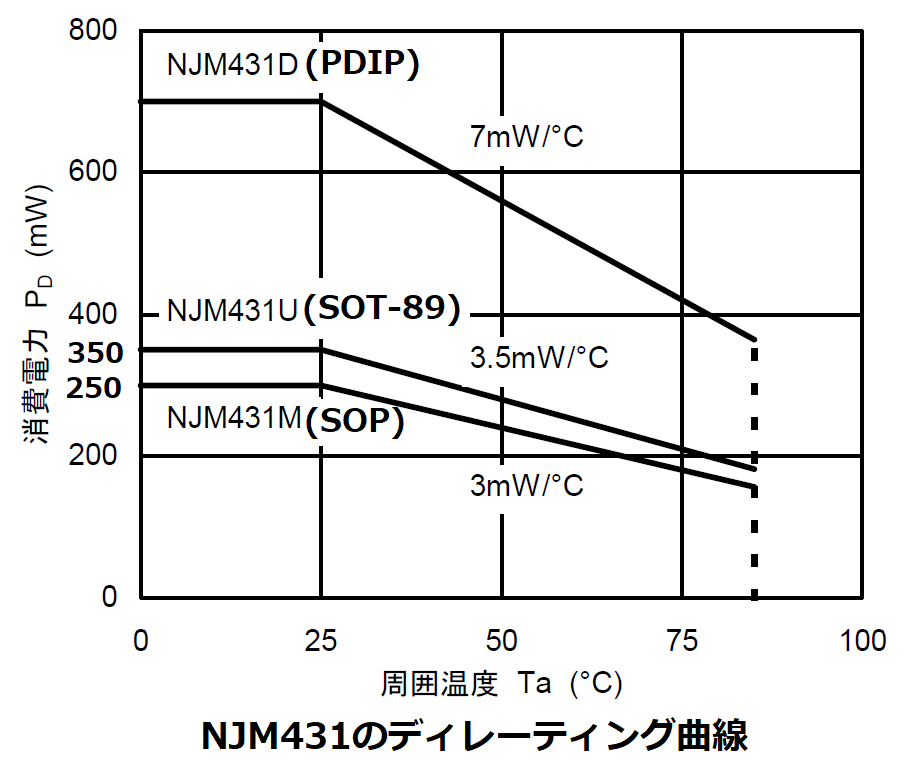

この許容損失ですが、TL491はデータシートに記載がないため、

ここではNJM431の値を参考にすると、SOT-89パッケージ品の場合、350mWとなります。

但し、この値は周囲温度Taが25℃までの場合であり、

ディレーティング曲線を見ると、温度上昇と共に低下するため、余裕を持たせる必要があります。

具体的には定格値にディレーティング率をかけて低下させた値より低くなるように動作させます。

許容損失のディレーティング率は一般的に50%なので、

350mW×0.5=175mW以下で動作するようにします。

ここでは、VKA=Vout=5Vで使用するので、175mW以下にするには、

IK=PD/VKA=175mW/5V=35mA

となり、カソード電流IKは35mA以内にする必要があります。

I2はR1=R2=5.1kΩなので、

I2=Vref/R2=2.495V/5.1kΩ≒0.5mA

となり、無負荷時のIinを求めると

Iin=IK+I2+Iout=35+0.5+0=35.5mA

以上から、Iinが35.5mA以下となるように、②式を変形してRinを決めます。

Rin=(VinーVout)/Iin=(12Vー5V)/35.5mA

≒197Ω

抵抗値はE24系列より、200Ωを選定した時のIinは

Iin=(VinーVout)/Rin=(12Vー5V)/200Ω

=35mA

R1の消費電力は

P=R1×Iin2=200Ω×(35mA)2=245mW

となり、定格電力が0.5Wの抵抗にすれば、

ディレーティング50%で250mWまで使用可能なのでOKです。

この回路の出力電流Ioutの最大値ですが、Ioutが増える分だけIKが減少します。

データシートには最低カソード電流1mAが規定されていますが、

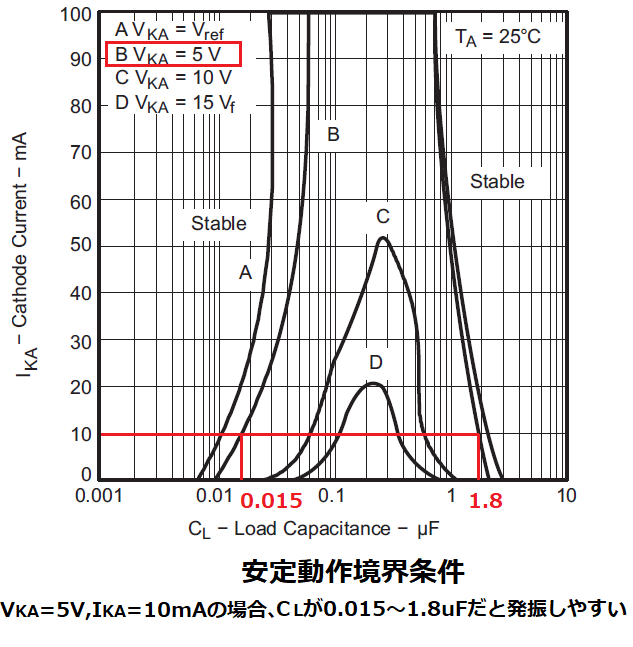

安定動作境界条件グラフを見ると、IKが小さいと発振(※)しやすくなるため、

最低でも5mA流すようにします。

※出力電圧が不安定になる現象で、IKが5mA、VKAが5Vの場合だと、

負荷容量CLが0.015~1.8uFの範囲で発生しやすくなります。

この範囲はIKを多く流すことで小さくでき、より動作が安定します。

従って、この回路の最大出力電流Iout(max)は

Iout(max)=IinーIK(min)ーI2=35ー5ー0.5=29.5mA

となります。

<出力コンデンサは不要>

シャントレギュレータのK-A間にコンデンサをつける必要は基本的にはありません。

コンデンサをつけてもノイズ除去効果は殆どなく、安定動作境界条件のグラフで説明した通り、

コンデンサ容量によっては出力が発振する恐れがあります。

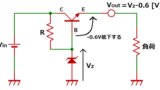

シリーズレギュレータ

基準電圧回路は出力電流が数十mA程度と小さいため、電源には不向きです。

この回路はトランジスタを組み合わせることで出力電流を大きくでき、電源として利用できます。

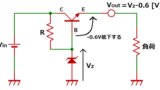

トランジスタのベースが下向きの配置なので、難しそうに見えますが、実は簡単な動作原理で、

トランジスタはベース電圧よりも約0.6V低い電圧がエミッタ電圧に出力されるように動作します。

このような動作になる理由ですが、トランジスタのB-E間はダイオードに置き換えて考えることができ、

NPNトランジスタの場合、ベースからエミッタへは順方向になるので、

ベース電圧VBに対し、エミッタ電圧VEはダイオードの順方向降下電圧VF分だけ低下します。

このVFはトランジスタのデータシートにベース・エミッタ間電圧VBEとして記載されており、約0.6Vです。

VBが一定を維持した状態で、エミッタからの負荷電流が増えてVEが低下した場合、

B-E間の電位差が大きくなるので、ダイオードに流れる電流(ベース電流)が増えます。

コレクタ電流は、IC=hFE×IBなので、その分電流が増え、負荷電流の増加を補うので、VEが上昇します。

VEが低下した場合は、これと逆の動作となり、以上から、B-E間が0.6V一定になるように動作します。

以上から、本回路構成では以下の関係式が成立します。

出力電圧Vout=シャントレギュレータのカソード電圧VKー約0.6V

シャントレギュレータは基準電圧回路の時と同様に、REF端子が2.495VになるIKを調整するので、

IKが増えればVKは低下し、IKが減れば上昇します。

従って、IKを制御することでVoutを一定値に維持することから、

基準電圧回路と同じ③式になります。

Vout=Vref × (R1+R2)/R2+Iref × R1 ③

この式を見てわかるようにVBE電圧の約0.6VはVoutには関係が無く、

高精度なシリーズレギュレータを構成できます。

シリーズレギュレータの詳細については下記記事で解説しています。

本例ではローム製トランジスタ2SCR533PR5を使用し、出力電流を100mA流すことができます。

このトランジスタは、IC=100mA時のhFEが300、VBE=0.65Vです。

Rin間の電圧は以下の式になります。

Vinー(Vout+VBE)=12ー(5+0.65)=6.35V

Rinを1.1kΩにした時の電流Iinは、

Iin=6.35V/1.1kΩ≒5.7mA

Iinは、シャントレギュレータのカソード電流IKとトランジスタのベース電流IBの合計なので、

シャントレギュレータの安定動作に必要なIK=5mAと、トランジスタがコレクタ電流ICを

100mA流すのに必要なベース電流IB=0.3mA(※)を十分確保できます。

(※IB=IC/hFE=100mA/300≒0.3mA)

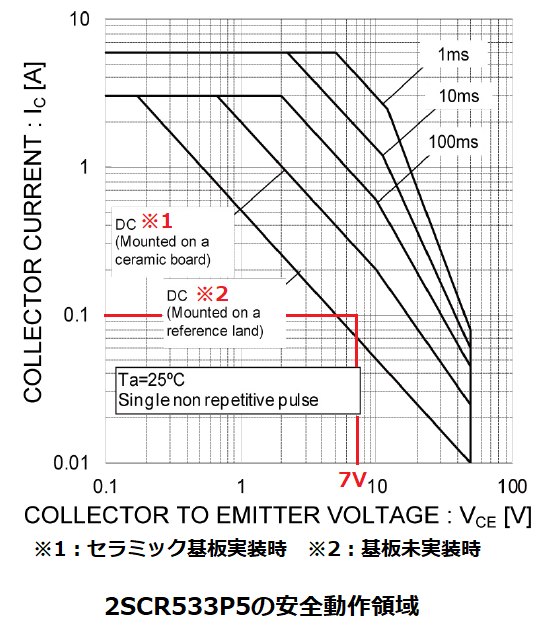

ここで注意する点としては、トランジスタの消費電力が許容損失を超えないかです。

トランジスタのコレクタ・エミッタ間電圧VCEは

VCE=VinーVout=12ー5=7V

なので、消費電力PDは

PD=VCE × IC=7V × 100mA=700mW

2SCR533P5の許容損失ですが、データシートを見ると、

0.5W(基板未実装時)~2W(セラミック基板実装時)と条件によってかなり差があります。

安全動作領域を見ると、VCE=7V、IC=100mAは2W(セラミック基板実装時)領域に入ることから、

一般的なガラスエポキシ基板に実装する場合、広めのパターンをとって放熱しやすくします。

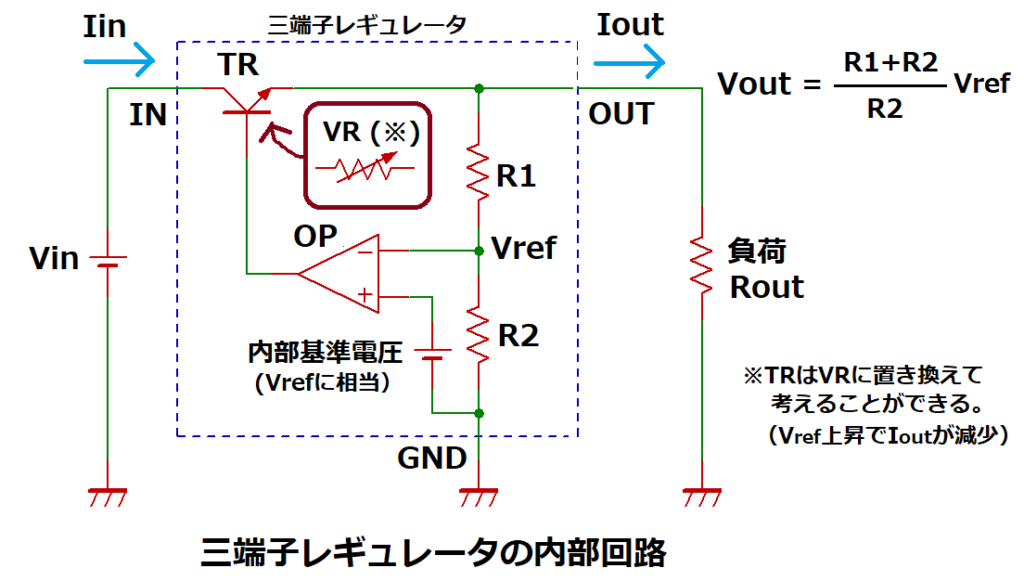

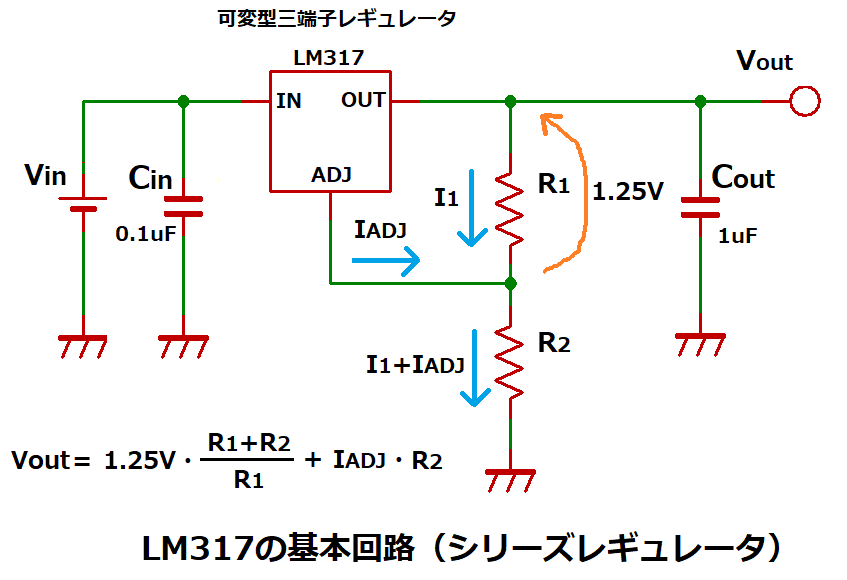

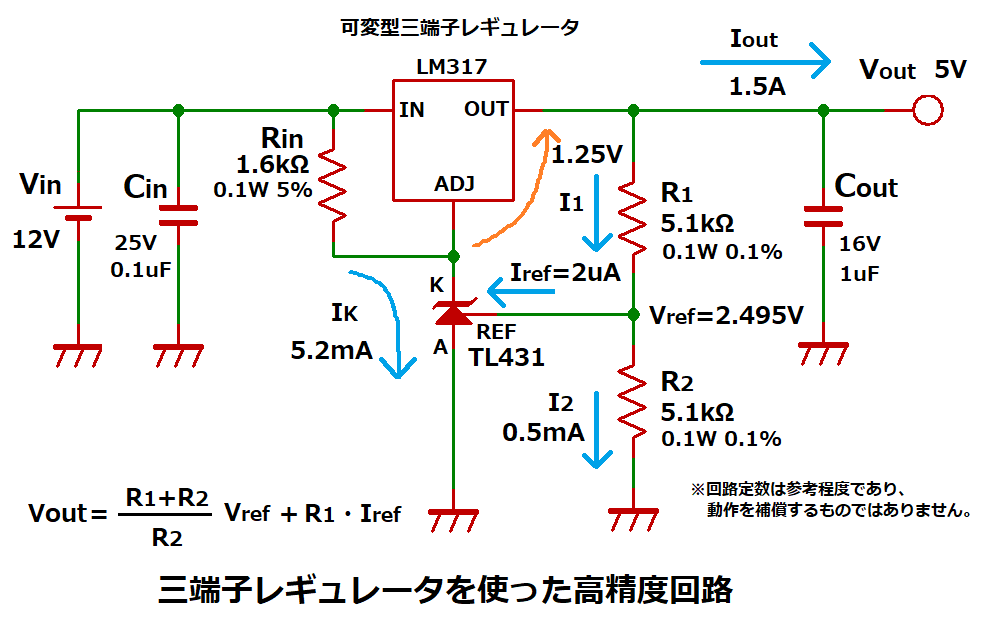

三端子レギュレータを使った高精度回路

上記のシリーズレギュレータ回路をトランジスタでなく、三端子レギュレータを使う方法です。

まずは、三端子レギュレータの基本回路を示します。

LM317はTI製の可変型三端子レギュレータで、

OUT端子とADJ端子間の電圧を1.25Vに維持するように動作します。

このLM317の基本回路における出力電圧は以下の式になります。

Vout=1.25V × (R1+R2)/R1+IADJ × R2

シャントレギュレータの③式と似ていますが、このADJ端子からの電流IADJは50uA程度と、

シャントレギュレータのIref=2uAより大きい分、設定精度が劣ります。

そこで、下図のようにシャントレギュレータと組み合わせることで③式が適用され、

高精度回路を構成できます。

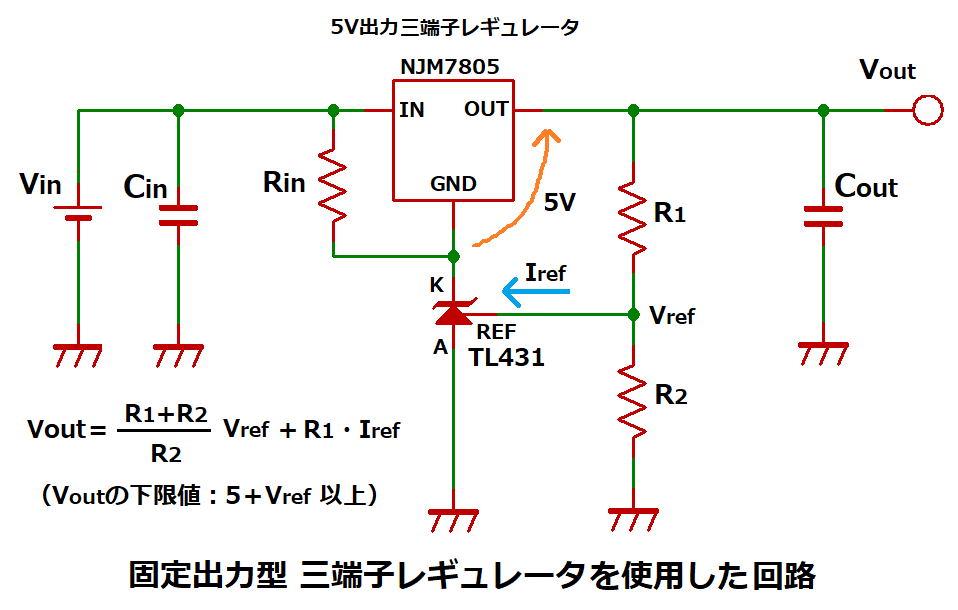

また、出力電圧が固定タイプの三端子レギュレータを組み合わせると、

出力電圧を変更することができます。(但し、Voutは(固定出力電圧+Vref)以上)

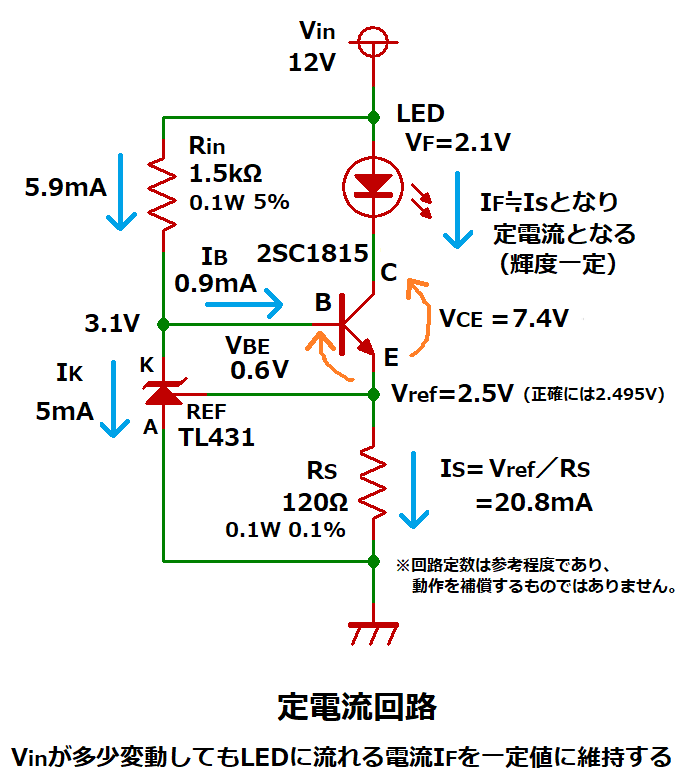

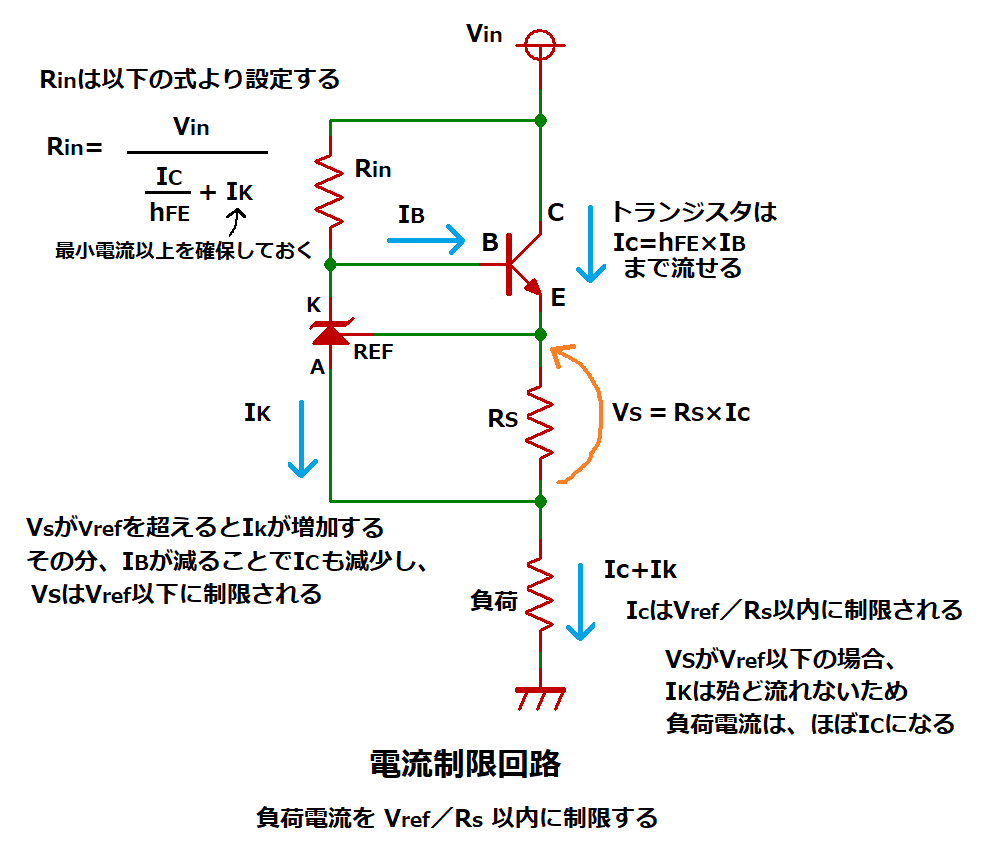

定電流源回路

定電流源として、負荷に一定の電流を流すことができます。

この回路例では入力電圧Vinが多少変動しても、

負荷であるLEDに流れる電流は一定なので、明るさが変化しません。

電流値ISは下記式になります。

IS=Vref/RS

この回路ではIS=20.8mAとなるので、LEDに流れる電流IFは約20mA(※)の一定値を維持します。

※厳密にはIS=IF+IBとなるため。

電流を一定にする仕組みですが、Vinが上昇した場合、ISが増加してREF端子電圧が上昇するため、

シャントレギュレータがIKを増加させると、その分ベース電流IBが減少し、

それによってトランジスタが流すことができるコレクタ電流が減少するため、ISが減ります。

Vin低下時はREF端子電圧が下がり、シャントレギュレータがIKを減少させることでIBが増加し、

トランジスタが流せるコレクタ電流が増えることでISが増えます。

以上の動作により、Vinが変動してもISを一定に維持できます。

Rinによって、シャントレギュレータに供給するIKとトランジスタのベース電流IBが決まります。

Rin間に印加される電圧はVinー(Vref+VBE)なので、流れる電流Iinは、

Iin=Vinー(Vref+VBE)/Rin

=12ー(2.5+0.6)/1.5kΩ

≒5.9mA

Vrefは正確には2.495Vですが、ここでは簡略化のため2.5Vとしています。

VBEは2SC1815(※)のデータシートより、IC=20mA時の値である0.6Vを使用しています。

※小信号トランジスタの定番品で、オリジナルの東芝製は廃止されていますが、セカンドソース品が多く入手しやすいです。

IC=20mAの場合の電流増幅率hFEはデータシートより150なので、必要なベース電流IBは、

IB=IC/hFE=20mA/150≒0.13mA

IBは入力電流Iinからカソード電流IKを引いた値になるので、

IKがシャントレギュレータの安定動作に必要な5mAが流れても、

IBは5.9ー5=0.9mAとなるので十分です。

次に、トランジスタの消費電力PCを計算します。

LEDのVFを2.1Vとすると、

VCE=Vinー(VF+Vref)

=12ー(2.1+2.5)=7.4V

なので、

PC=VCE × IC=7.4V × 20.8mA ≒ 154mW

となり、2SC1815の許容損失は周囲温度60℃でも250mWあるので問題ありません。

LEDの使い方については下記記事で解説しています。

この定電流回路を応用し、負荷電流をVref/RSに制限する過電流保護を行うこともできます。

但し、制限する負荷電流を大きくする場合、RSでの消費電力が大きくなるため、

Vrefが1.25Vなどの低電圧タイプのシャントレギュレータにした方が低損失で、

負荷への入力電圧降下も低くできます。

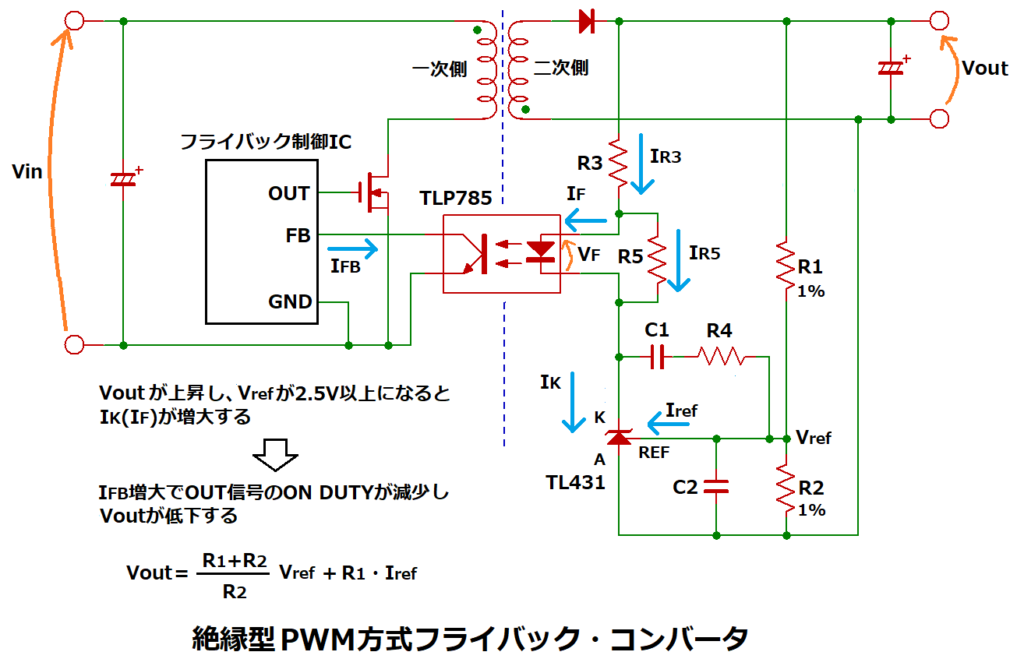

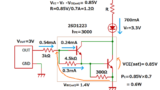

二次側出力電圧制御回路

絶縁型スイッチング電源の二次側出力電圧制御を行う回路です。

本例はフライバック電源での適用例ですが、フォワード電源やLLCコンバータ等、

高精度の出力電圧が要求される絶縁型電源の殆どがこの方式を使用しています。

この回路は基準電圧回路と同じく、REF端子電圧がVref(2.5V)に維持されるように

カソード電流IKが増減することで、フォトカプラへの入力電流IFも変化します。

これによって、一次側にあるフォトカプラ出力で流せる電流が変化するので、

フライバック制御ICはFB端子から流れ出るフィードバック電流IFBの電流量に応じて、

FETのON時間の割合(ON DUTY)を変化させることで出力電圧が変化します。

具体的には以下の動作になります。

Vout(Vref)上昇 → IK(IF)増加 → IFB増加 → ON DUTY減少 → Vout(Vref)低下

※Voutが低下した場合は逆の動作になります。

フライバック電源の動作原理については下記記事で解説しています。

フライバック制御ICに関わらず、一般的な電源制御ICは、このIFBが増加すると

ON DUTYやスイッチング周波数を変化させて出力電圧が低下する動作を行うため、

フライバック電源以外でも二次側回路は同様の構成となります。

二次側出力電圧は基準電圧回路と同じ③式になります。

Vout=Vref × (R1+R2)/R2+Iref × R1

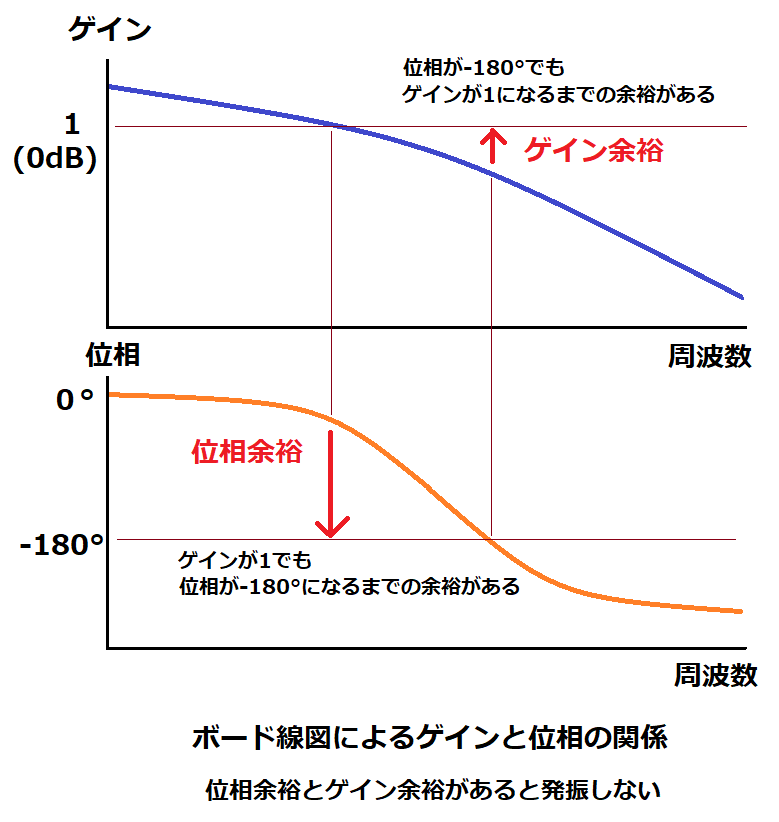

C1とR4は位相補償回路で、出力電圧の発振(振動)を防止します。

位相補償が必要になる理由ですが、出力電圧の制御は一次側にある制御ICが行うことから、

実際に出力電圧が変化するまで応答が遅れます。

発振は、この応答(位相)の遅れが原因で発生します。

具体的には、出力から入力へのフィードバック信号の位相が180度遅れ、

ゲインが1以上あると発振します。

この位相の遅れは周波数の上昇と共に大きくなる特性を持つことから、

位相補償回路によって、位相の遅れが大きくなる高周波領域のゲインを下げて発振を防止します。

位相補償回路の詳細は下記記事で解説しています。

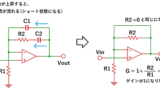

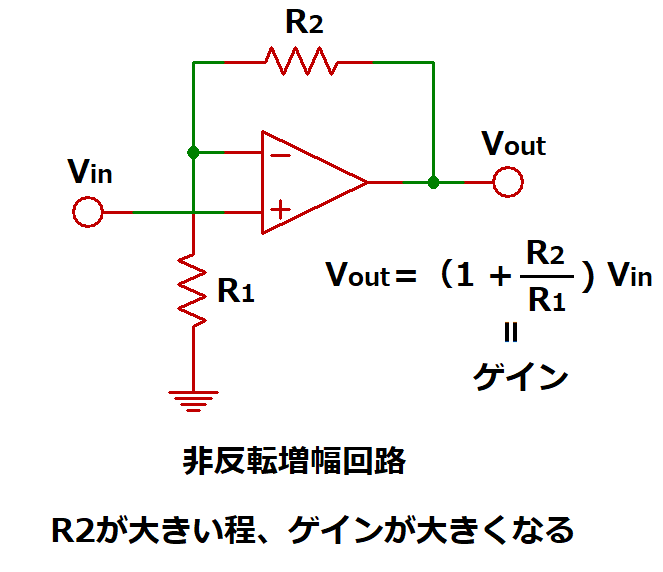

ゲインの大きさはフィーバック信号間の抵抗値が大きい程大きくなります。

理由はオペアンプの非反転増幅回路のゲインの式から理解することができます。

シャントレギュレータもオペアンプが内蔵されているので、動作としては同じです。

非反転増幅の詳細は下記記事で解説しています。

この回路では、シャントレギュレータの出力であるカソード(K)と

リファレンス入力(REF)間の抵抗が大きい程、ゲインが大きくなります。

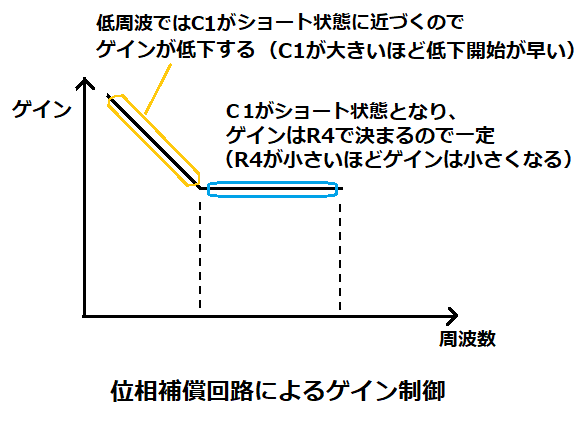

フィードバック信号が直流だと、C1によりKとREF間はオープン状態になるので、

KーREF間抵抗は無限大と考えることができるため、ゲインは非常に大きいです。

フィードバック信号の交流成分については、

周波数が高いほどC1のインピーダンスZ=1/jωCが低下することで、オープン状態ではなくなり、

R4とC1の合成抵抗値(※)でゲインが決まるため、周波数上昇と共にゲインが低下します。

更に高周波ではC1が完全ショートとなり、R4だけの抵抗値になるのでゲインは一定になります。

(※話を簡略化するため、ここではインピーダンス=抵抗で説明してます)

以上から、C1が大きい程、より低周波でゲインが低下し、

R4が小さい程、高周波領域でのゲインを小さくできます。

しかし、ゲインを小さくし過ぎると応答性が悪くなることから、

発振しない程度にゲインを確保するように、C1とR4を調整します。

C1とR4の値については、制御ICの特性やフォトカプラの変換効率などに影響されるため、

一義的に決めることはできず、実機にて調整しながら求めることになりますが、

以下の範囲内に設定される傾向があります。(あくまで参考程度)

C1: 0.01uF~1uF

R4: 0Ω~20kΩ

実機での調整は出力電圧波形を見て行いますが、定常動作時はもちろんのこと、

動作中に負荷変動(無負荷⇔フル負荷)が発生した場合の出力電圧変動や、

起動時の立上り時間や電圧上昇波形についても確認する必要があります。

C2については基本的に不要ですが、イミュニティ対策(ノイズによる誤動作防止)で

100pF程度を設ける場合があります。

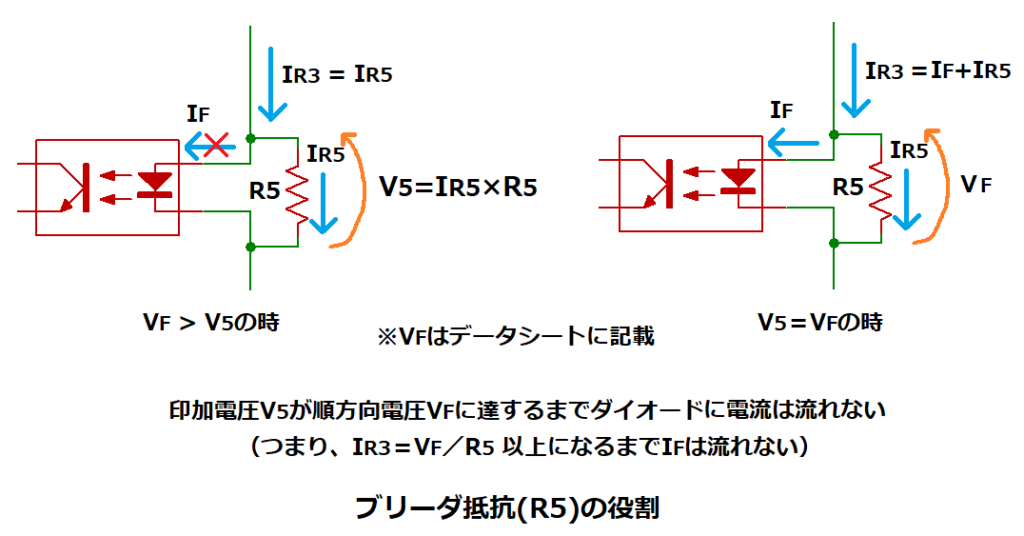

R5はブリーダ抵抗などと呼ばれ、微小電流のうちはフォトカプラが動作しないようにするために

1kΩ~10kΩ程度を設けることがありますが、これも無くても良い場合が多いです。

ブリーダ抵抗については下記記事で解説してます。

R3によってフォトカプラとシャントレギュレータに流れる電流IKとIFが決まります。

厳密にはIR5も含まれますが、微小で一定値なので、IK≒IFとなります。

IFに必要な電流については、IFBにどれくらい電流を流したいかで決まります。

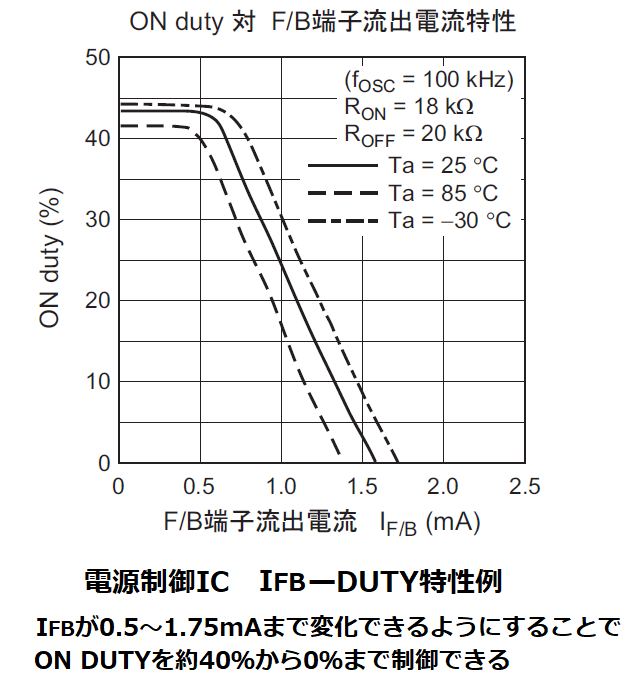

このフライバック制御ICのDUTY制御にIFBが1.75mA以上確保する必要がある場合、

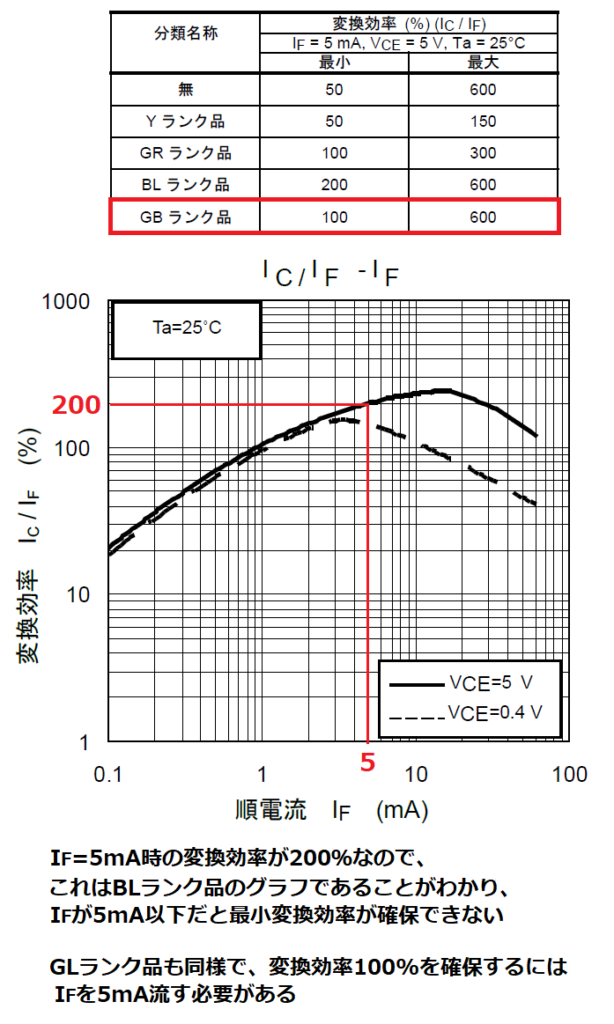

フォトカプラの変換効率(IC/IF)から必要なIFを求めます。

TLP785のGBランク品の変換効率は100~600とありますが、

この値はIF=5mAで周囲温度25℃の時であり、IFが小さかったり、温度が高いと低下するので、

IFが5mA流れるようにすることで変換効率100%を確保し、IFBも5mAまで流すことができます。

IKについては、IK≒IFになることから、IFを5mA流すことで、

TL431の安定動作に必要な最低カソード電流IK(1mA)以上になるのでOKとします。

ここではVoutを12Vとした場合のR3を求めてみると、

IF=5mA時のVFはTLP785のデータシートより1.1V、VKA=Vrefとした場合、

R3=(VoutーVFーVKA)/IF

=(12ー1.1ー2.5)/5mA

≒1.6kΩ

ここでR3の消費電力は

P=R3×(IF)2=1.6kΩ×(5mA)2=40mW

となり、定格電力0.1Wの抵抗を選定した場合、

ディレーティング50%で50mWまでOKなので問題ありません。

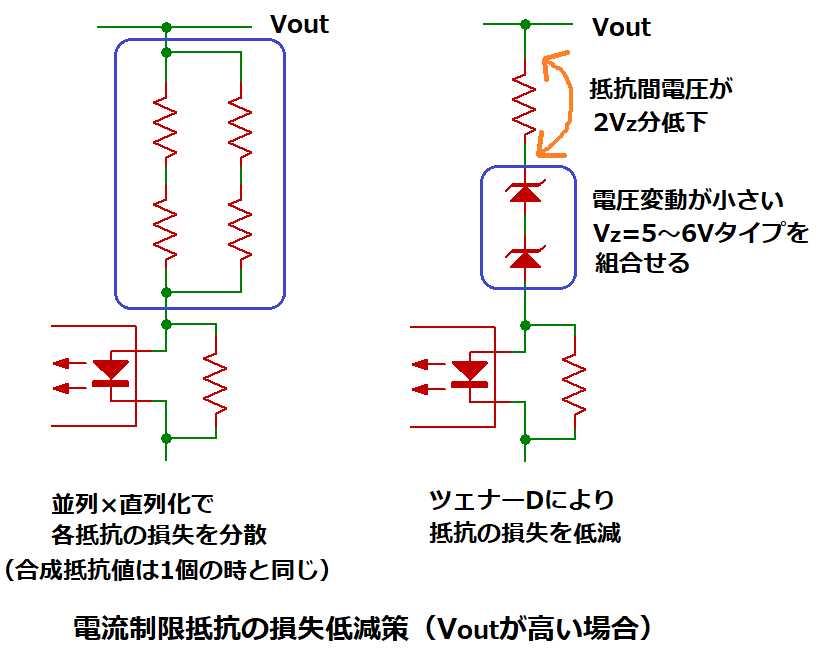

このR3の消費電力はVoutが高いと増加するため、必要に応じて抵抗を並列接続したり、

ツェナーダイオードを直列接続することで、抵抗間電圧を低くして消費電力を下げます。

TL431を使った応用回路

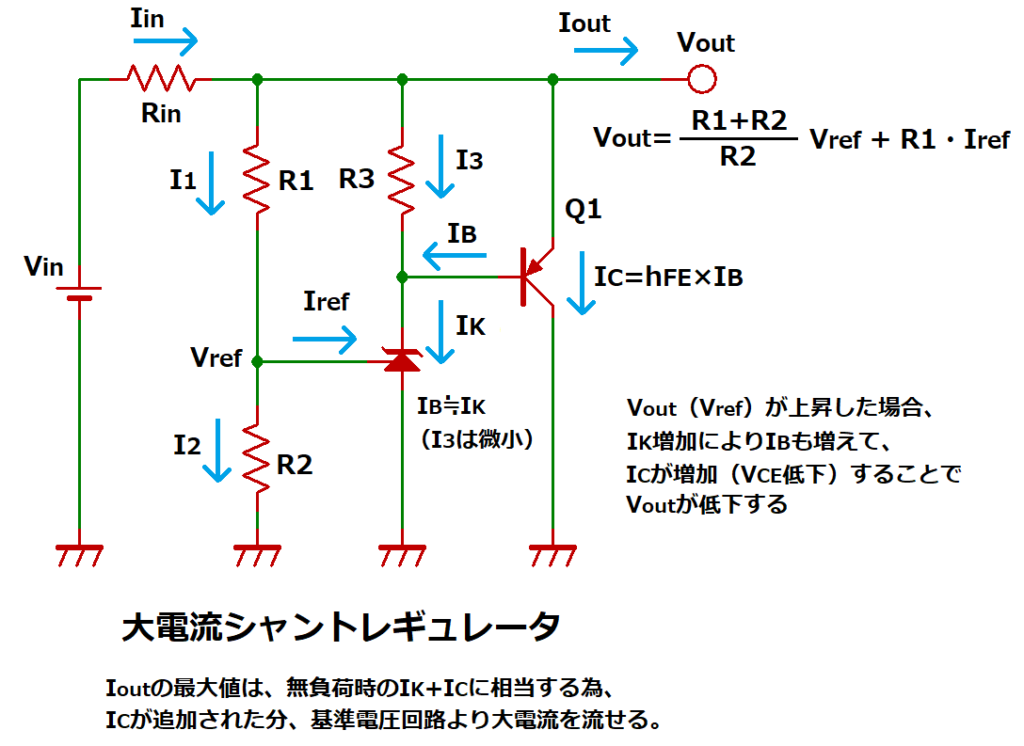

大電流シャントレギュレータ

基準電圧回路では、出力電流Ioutはカソード電流IKと相反する関係であり、

Ioutの最大値は、ほぼIKの最大値になることから、

IoutはTL431の最大カソード電流である100mA以上にすることはできません。

本回路では、出力電流を最大カソード電流以上にするために、

基準電圧回路にPNPトランジスタ(Q1)を追加したもので、

Ioutの最大値をIK+ICまで増加できます。

抵抗値の決め方ですが、Rin、R1、R2については基準電圧回路と同じで、

R3はベース・エミッタ間抵抗なので、通常は1~10kΩ程度を選びます。

ベース・エミッタ間抵抗の決め方については下記記事で説明しています。

記事はNPNトランジスタの場合ですが、PNPも同様です。

Q1の選定については、軽負荷時ほど発熱が高くなるので、

消費電力がトランジスタの許容損失の50%以内に収まるようにします。

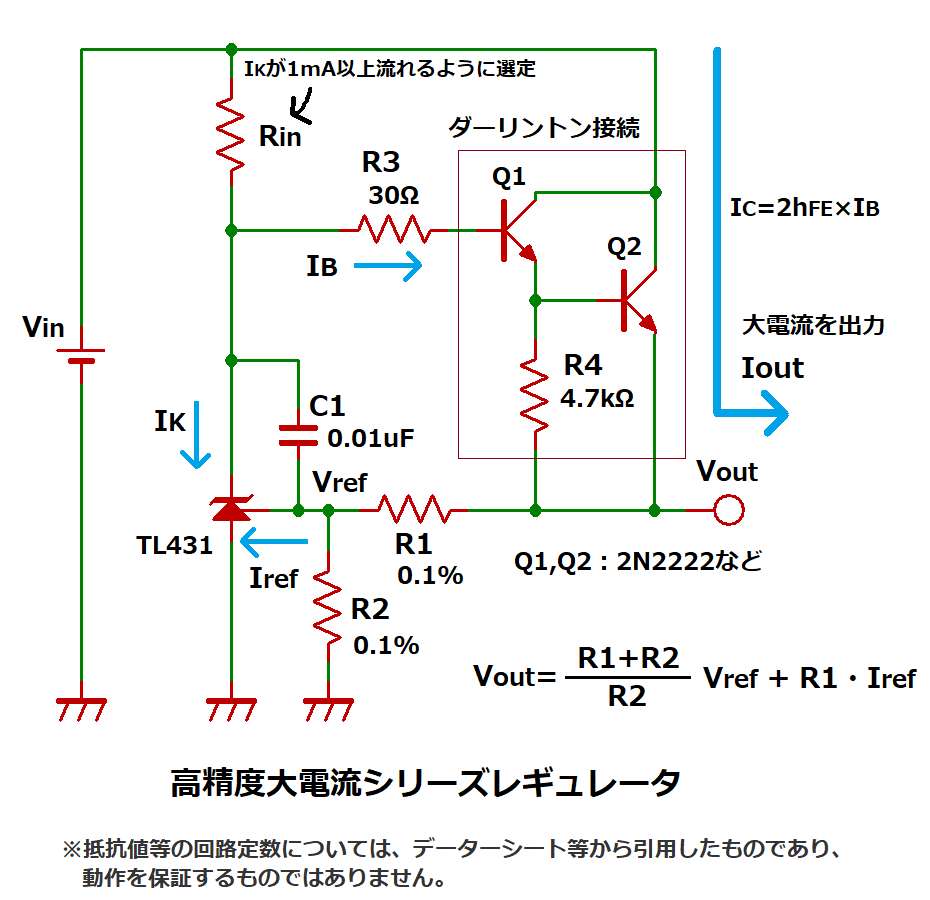

高精度大電流シリーズレギュレータ

前述したシリーズレギュレータにトランジスタをもう1個追加し、

Q1とQ2をダーリントン接続することで、大電流出力を可能にしています。

ダーリントン接続については下記記事で解説してます。

この回路は入出力間の電位差(VinーVout)が大きくなる欠点がありますが、

電流増幅率hFEを2倍にできるので、少ないベース電流IB(IK)で大電流を出力できます。

この例では、Q1、Q2を最大コレクタ電流が600mAと大きい2N2222を使用しています。

Rinはシャントレギュレータの最小電流1mA以上を確保するように設定します。

Rin=(Vinー(Vout+2VBE))/IK

C1は発振防止、R3はベース電流制限、R4はQ2の動作安定用です。

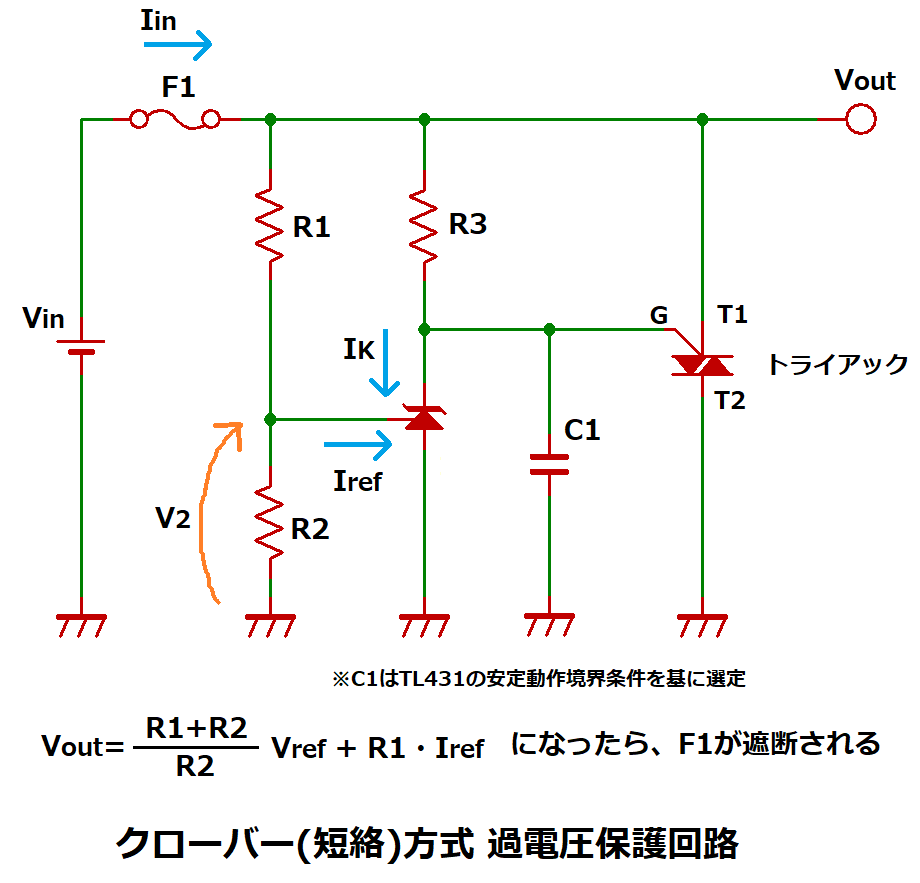

クローバー(短絡)方式 過電圧保護回路

入力電圧が制限値を超えた時にトライアックをオン(短絡)させ、

ヒューズF1を遮断させることで、Vout以降の回路に過電圧が印加されることを防ぎます。

R1とR2は入力電圧が制限値以内の時はV2がVref(2.5V)以下になるように設定します。

この時、カソード電流IKはゼロなので、トライアックのゲートGとT1は同電位となり、

トライアックはオフです。

入力電圧が増加し、V2がVrefを超えるとカソード電流IKが流れることで、

トライアックのゲート電圧Gが低下します。

この電圧低下がトライアックのゲートトリガ電圧を超えるとトライアックがオンします。

トライアックは一度オンしたら、流れる電流が保持電流以下になるまでオフしないため、

ヒューズF1に流れる電流Iinが急増し、ヒューズの溶断電流を超えると遮断されます。

ヒューズの選定については下記記事で解説しています。

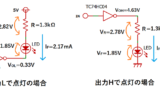

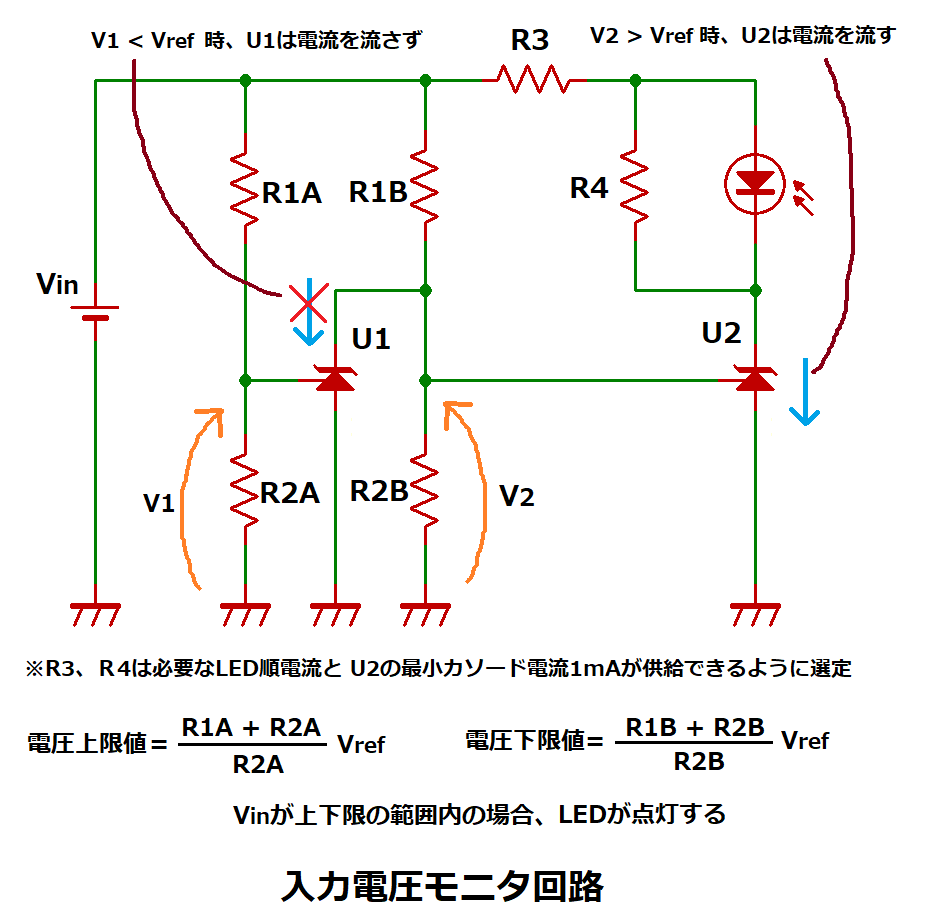

電圧モニタ回路

入力電圧が規定範囲内の時にLEDが点灯する回路で、

バッテリー電圧の状態表示などに利用できます。

この回路は電圧V1がシャントレギュレータの基準電圧Vref以下であれば、

U1のカソード電流は殆ど流れないので、U1は無いものとして考えることができます。

この時、V2はVinをR1BとR2Bの分圧比で決まるので、V2がVref以上の時、

U2のカソード電流が流れることで、LEDは点灯します。

次にVinが上昇し、V1がVrefを超えるとU1のカソード電流が流れることで、

V2は低下してVref以下になったら、U2のカソード電流が止まり、LEDは消灯します。

R3はLEDが必要な輝度を得ることができるLED順電流と、

U2の動作安定に必要な最小カソード電流1mA以上を確保できる抵抗値にします。

R4は先程、二次側出力電圧制御回路で説明したブリーダ抵抗です。

これは、V2がVrefより低くても、U2に微小電流が流れた際に、

LEDがわずかに点灯(暗点灯)してしまうことを防ぐため、

R4側に電流を流してLEDが点灯しないようにします。

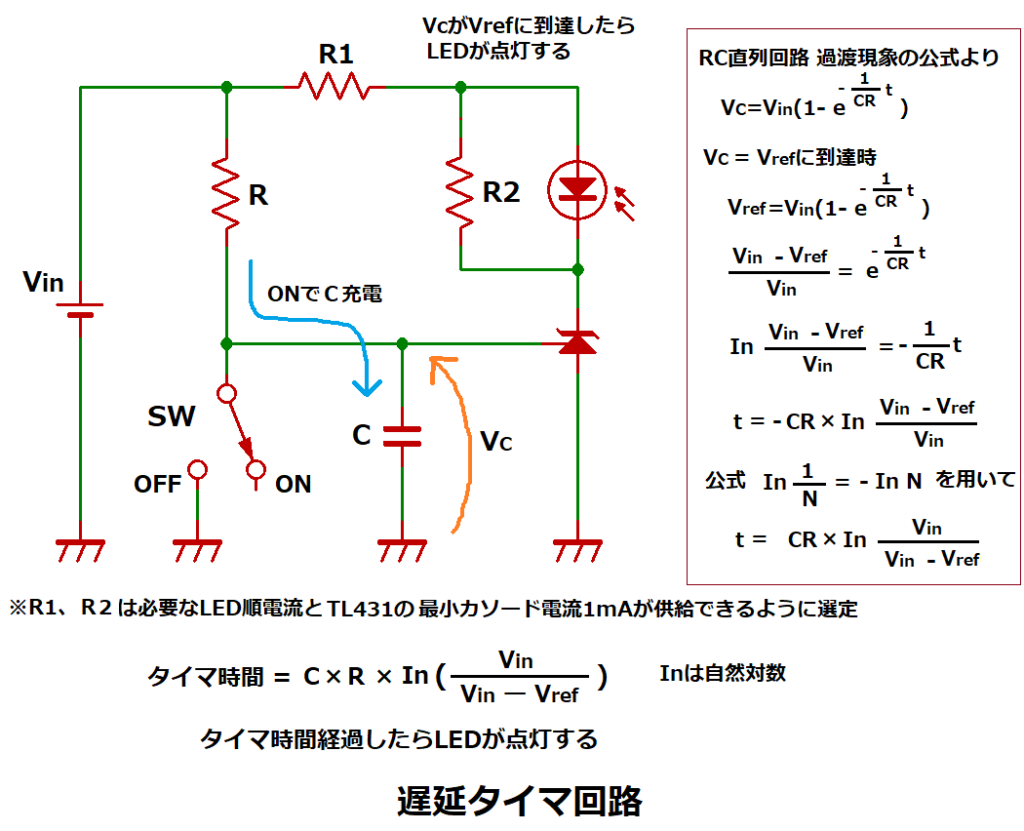

遅延タイマ回路

スイッチONで、一定時間経過後にLEDが点灯する回路です。

RC直列回路のコンデンサ充電電圧が基準電圧Vrefに到達したら、

シャントレギュレータに電流が流れ、LEDが点灯する仕組みで、

点灯するまでのタイマ時間は時定数CRで決まります。

R1とR2の決め方は、上述の入力電圧モニタ回路と同様です。