この記事でわかること

・ブートストラップ回路の動作がわかる

・コンデンサ、ダイオード等の選び方

・デメリットと使用上の注意点について

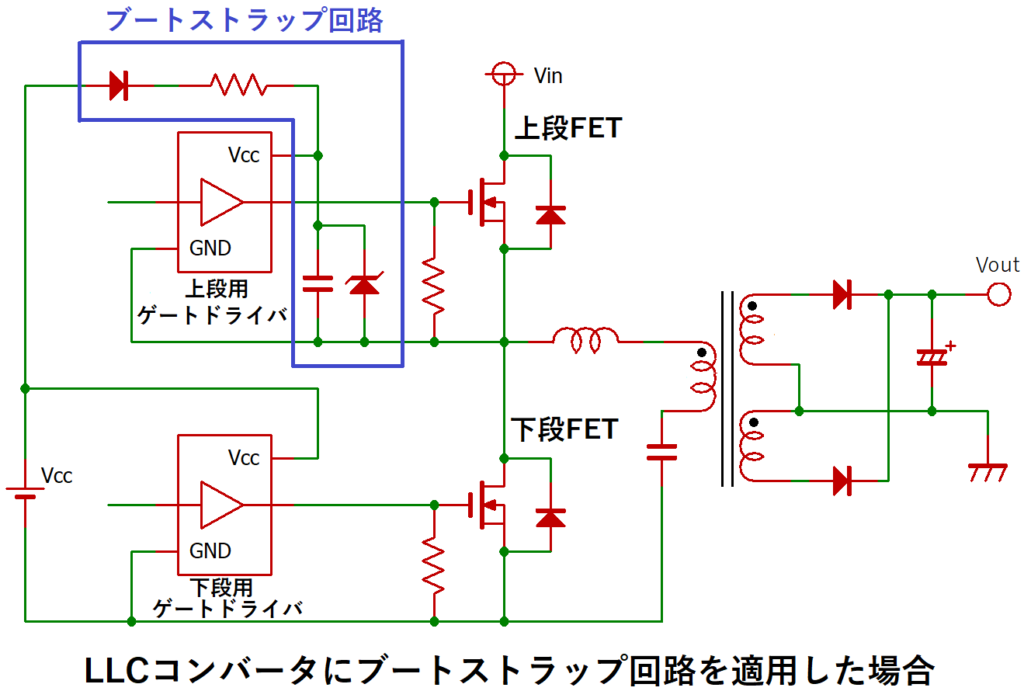

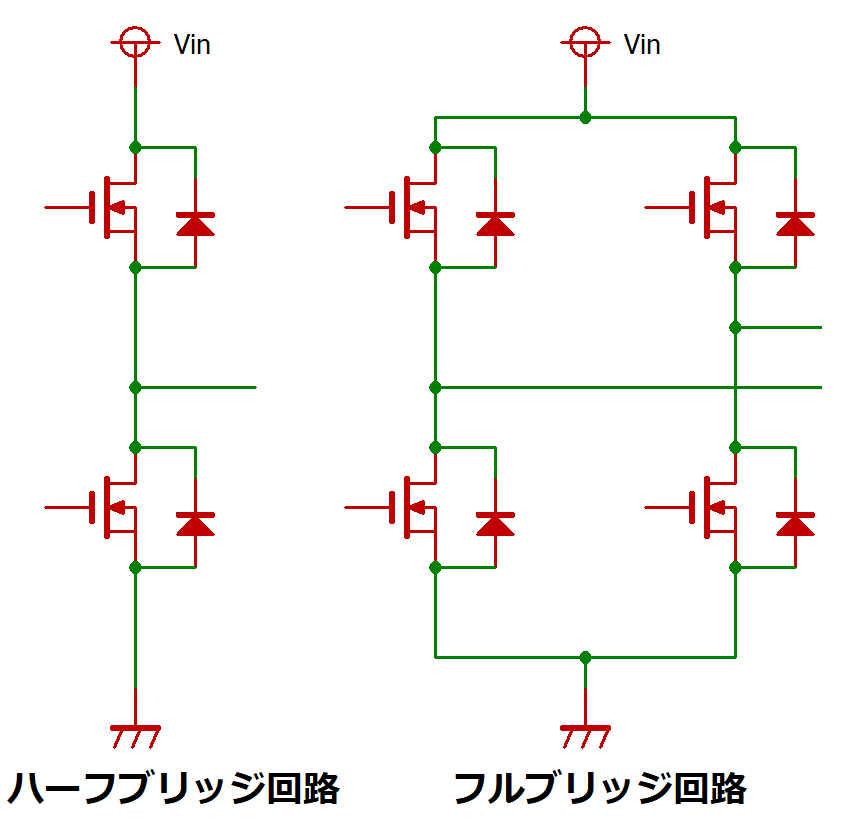

ブートストラップ回路は、FETを2段構成(※1)にした場合、

上段FET用のゲートドライバに電源を供給するための回路です。

※1:ハーフブリッジ回路と呼ばれ、

LLCコンバータなどの電源回路やモータ駆動回路に用いられます。

また、これを2個組み合わせたものをフルブリッジ回路と呼びます。

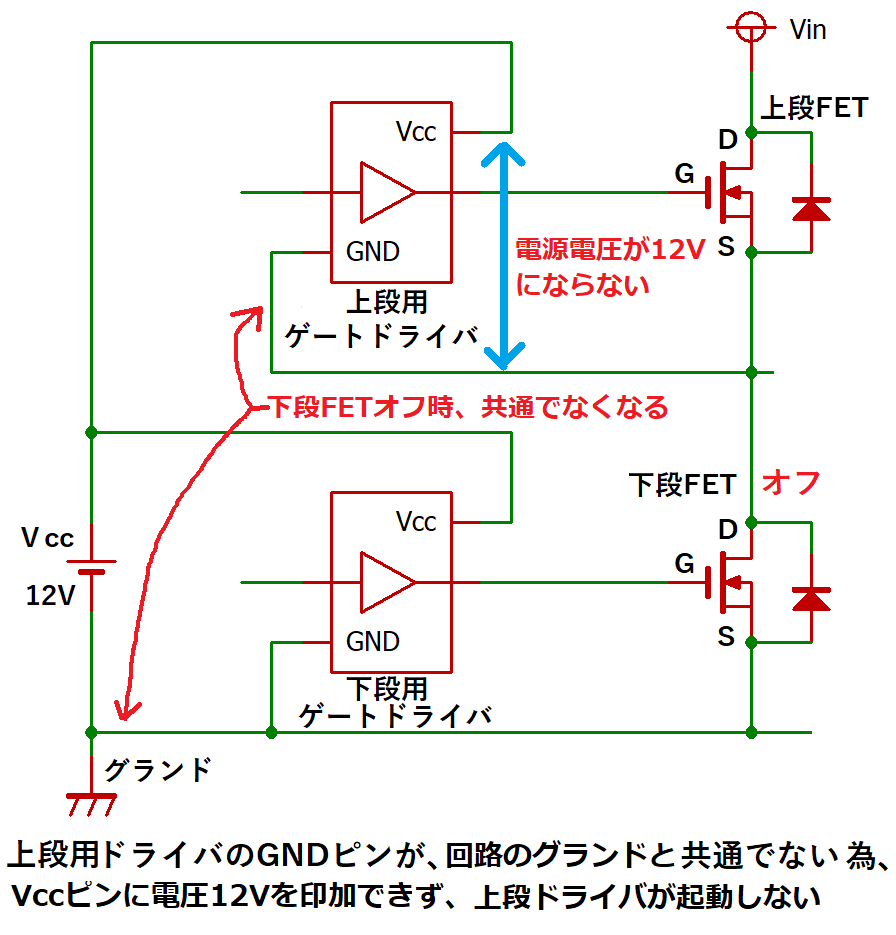

ゲートドライバはゲート・ソース間に電圧を印加することで、FETをオンさせます。

このため、上段用ゲートドライバのGNDピンは上段FETのソースと接続する必要があります。

このGNDピンは回路のグランドと共通でない為、

上段用ゲートドライバの電源供給に、

下段と同じ電源Vccをそのまま使うことができません。

ブートストラップ(Bootstrap)とは、「自力で~する」という意味であり、

FET自らのスイッチング動作により、電源を供給する事ができます。

本記事では、ブートストラップ回路の動作原理と、

その設計方法について解説します。

ブートストラップ回路が必要な理由

通常、パワーMOSFETのゲート・ソース間電圧VGSは10~15Vです。

マイコン等からの3.3Vや5V信号ではFETを制御できないため、(※2)

ゲートドライバで10~15V信号に変換してから入力します。

※2:ゲートドライバは電圧を高くするだけでなく、

出力電流も大きくすることでゲート電圧の立上りを早くできます。

このゲートドライバに電源Vcc=12Vを供給する場合を考えます。

下段用ゲートドライバのGNDピンは回路のグランドと共通なので、

電源ピンには12Vがそのまま印加されます。

一方、上段ゲートドライバのGNDピンについては、

下段FETがオンすれば、グランドと共通(※3)ですが、

オフすると、グランドから切断されます。

※3:厳密にはFETにはON抵抗があるので、完全なショート状態ではありませんが、

ON抵抗値は非常に小さいため、ここではグランドと共通とします。

このため、電源Vcc=12Vを電源ピンに入力しても、

電源電圧は12Vにならず、ドライバを動作させることができません。

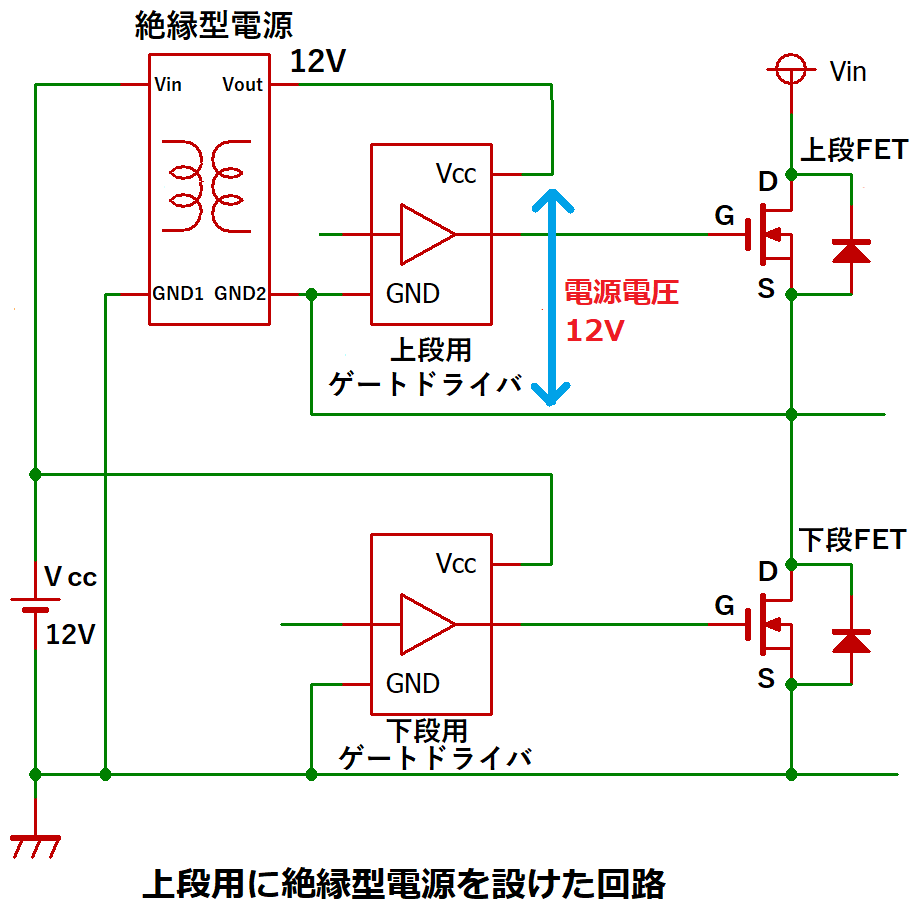

このため、上段専用の12V電源を設けます。

この電源の出力グランドは上段ドライバのGNDに接続するため、

絶縁型電源にする必要があります。

しかし、上段ドライバを動作させるだけの為に絶縁型電源を設けるのは、

コスト・サイズを考えると、もったいないです。

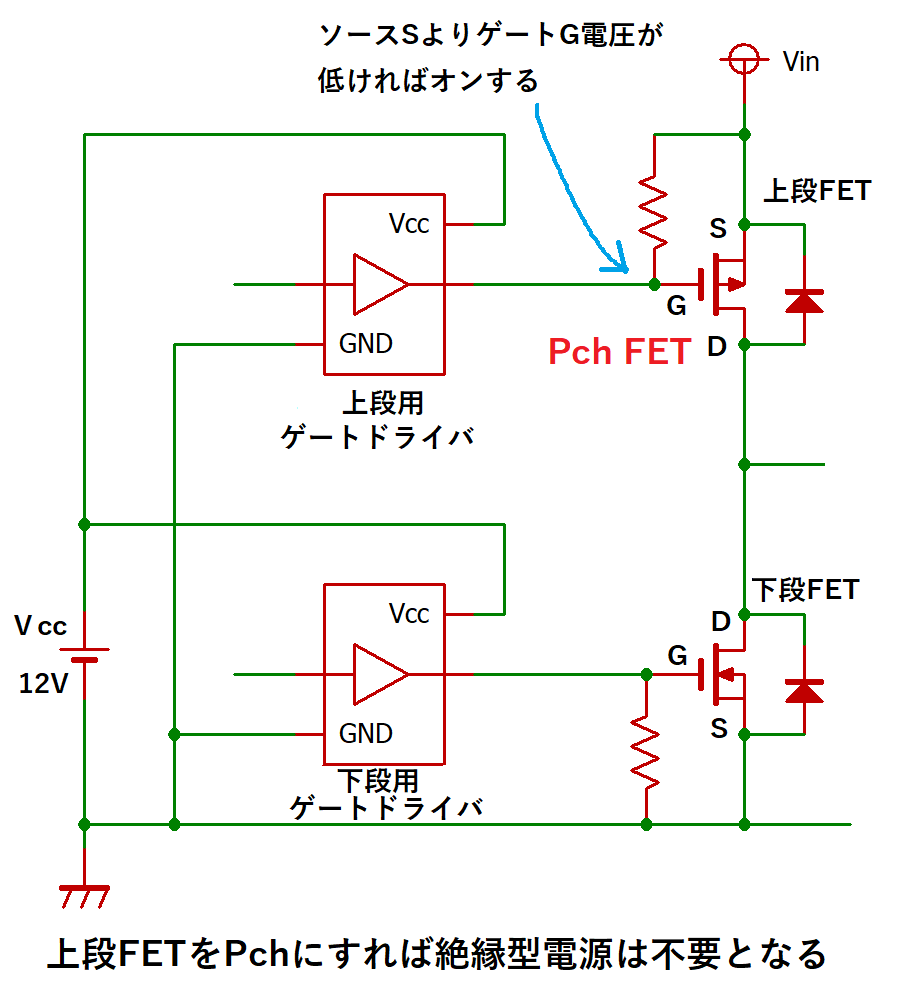

絶縁型電源を設けたくない場合は、

上段FETにPch FETを使用する方法があります。

Pch FETは、ソース(S)よりゲート(G)の電圧が低ければオンするので、

ゲートドライバのグランドをソースに接続する必要がありません。

つまり、上段用ゲートドライバのGNDピンを回路のグランドに接続できるので、

下段用ゲートドライバと同じ電源Vccを使用できます。

この方法が、回路的にはスッキリするのですが、

Pch MOSFETは、その特性上、ON抵抗やゲート容量が大きい等、Nch FETより性能が劣ります。

ハーフブリッジ回路では、上下FETの特性が同じでないと問題が発生します。

ゲート容量が違うということは、ターンオン/オフ時間が違ってくるため、

上下の動作タイミングがずれると、両方が同時オンしてしまい、

貫通電流が流れてFETが壊れます。

また、Pch FETは性能が悪く、用途も限定されることから、

製品として種類が少なく、あったとしても価格が高いです。

このため、上下とも同じNch FETが使え、

かつ絶縁型電源が無くても良い方法として、

ブートストラップ回路が必要なのです。

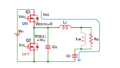

ブートストラップ回路の動作原理

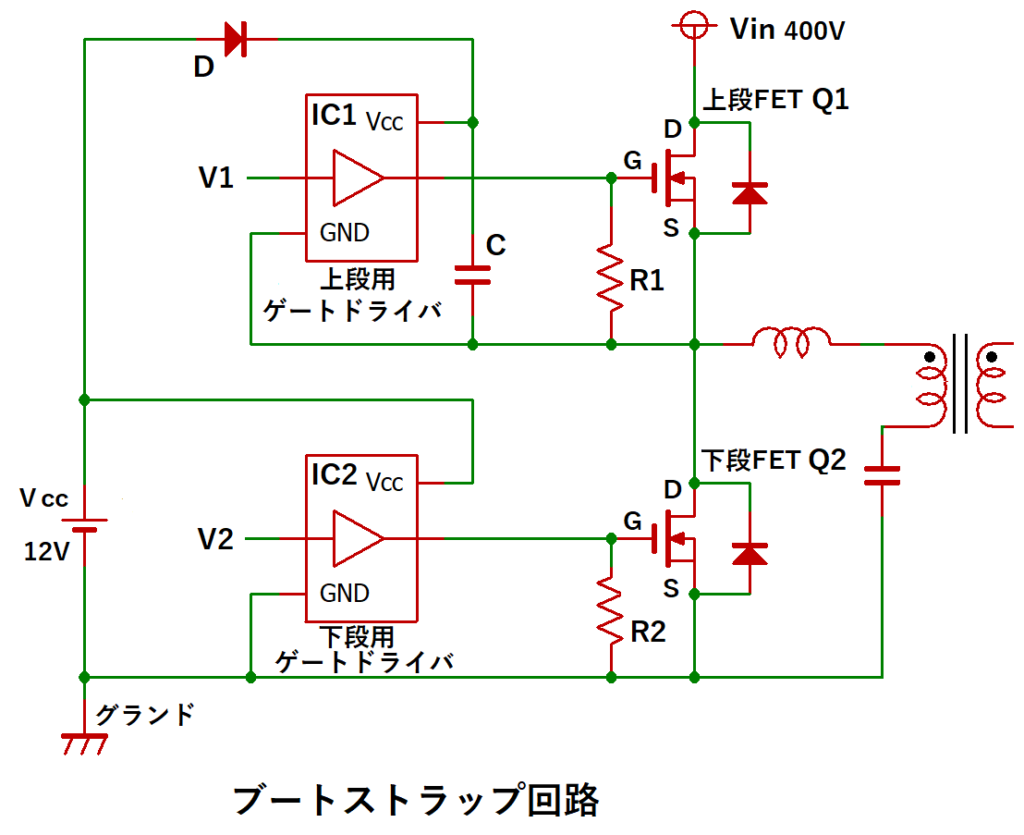

ブートストラップ回路の基本構成はダイオードとコンデンサであり、

必要に応じて、抵抗やツェナーダイオードを追加しますが、

動作を分かりやすくする為、ここでは基本構成で説明します。

この例では、LLCコンバーターを例にして、

ハーフブリッジ回路への入力電圧Vin=400V、

ゲートドライバへの電源電圧Vcc=12Vとします。

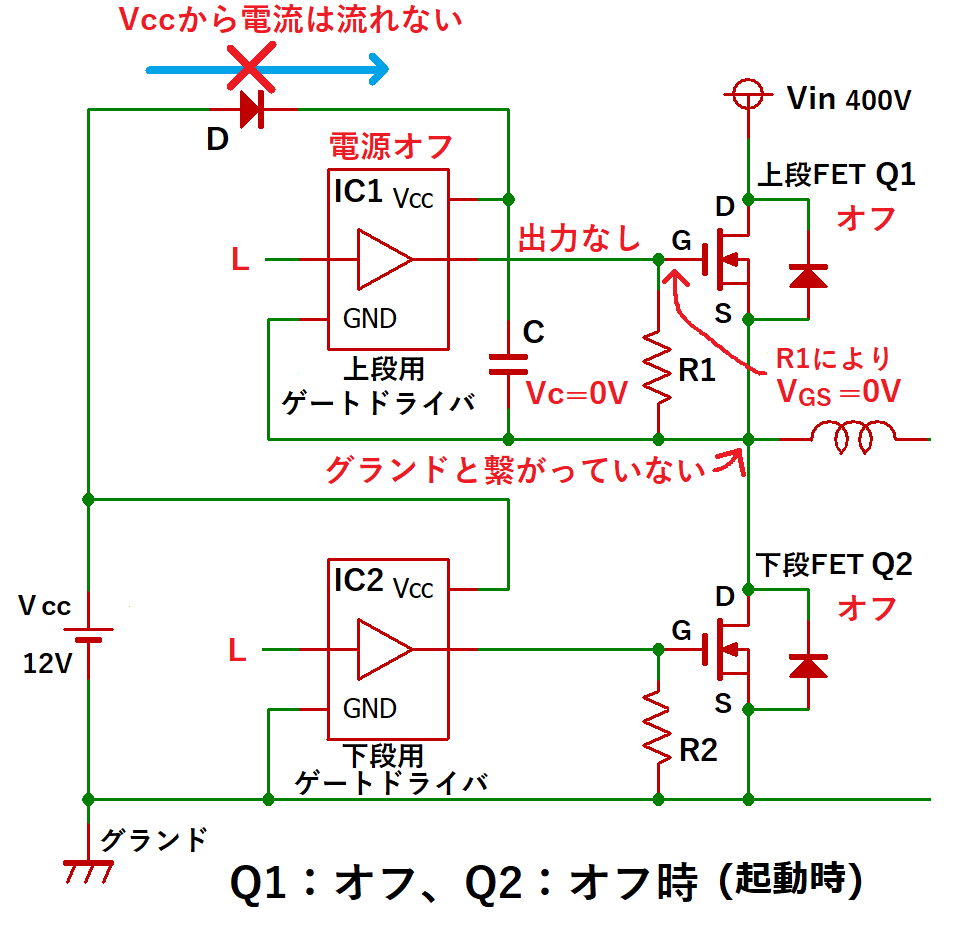

1.Q1:オフ、Q2:オフの時

起動時の状態になります。

この時、上段ゲートドライバ(以下、IC1)のGNDピンはグランドと繋がっておらず、

電源Vccから電流は流れない(つまり、電源が供給されない)ため、IC1は動作しません。

しかし、Q1にはゲート・ソース間抵抗R1が接続されているので、

IC1からゲート信号が出力できなくても、

ゲート電圧VGSはゼロとなるので、Q1はオフとなります。

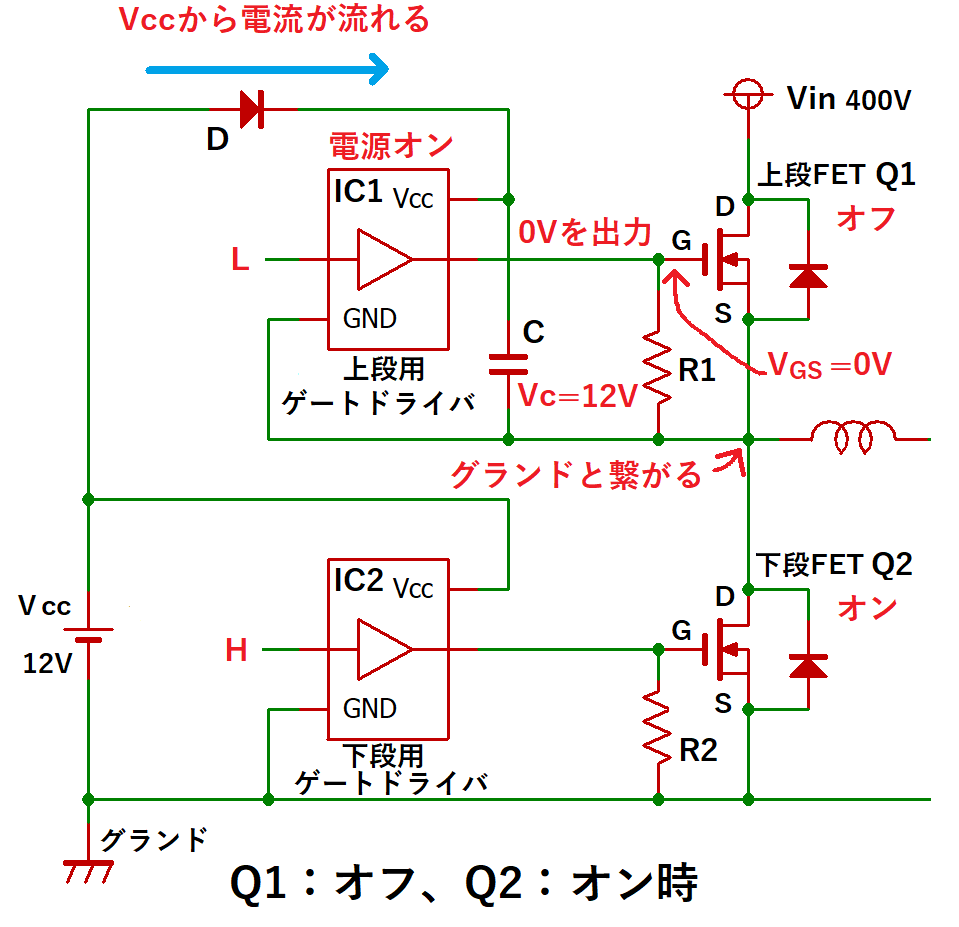

2.Q1オフ、Q2:オンの時

Q2がオンするので、IC1のGNDピンがグランドと共通になります。

厳密にはQ2のON抵抗があるので、完全なショートではありませんが、

ON抵抗値は数Ωと非常に小さいため、ここではグランドと共通と考えます。

これによって、IC1のGNDピンはグランドとつながるので、

電源Vccから、IC1の電源ピンに電流が流れ込むので、

12Vが供給され、IC1が起動します。

IC1への供給電圧ですが、

ダイオードDの順方向電圧VFによる電圧降下があるので、

厳密には12VよりVF分低下しますが、VF=1V程度と小さいので、ここでは無視します。

IC1が起動すると、ゲート信号が出力されますが、

この時のIC1への入力信号はLなので出力信号もLとなり、Q1はオフのままです。

この時、コンデンサCにも電流が流れて充電されます。

Q2のオン時間が十分長ければ充電が完了し、Cの電圧は12Vになります。

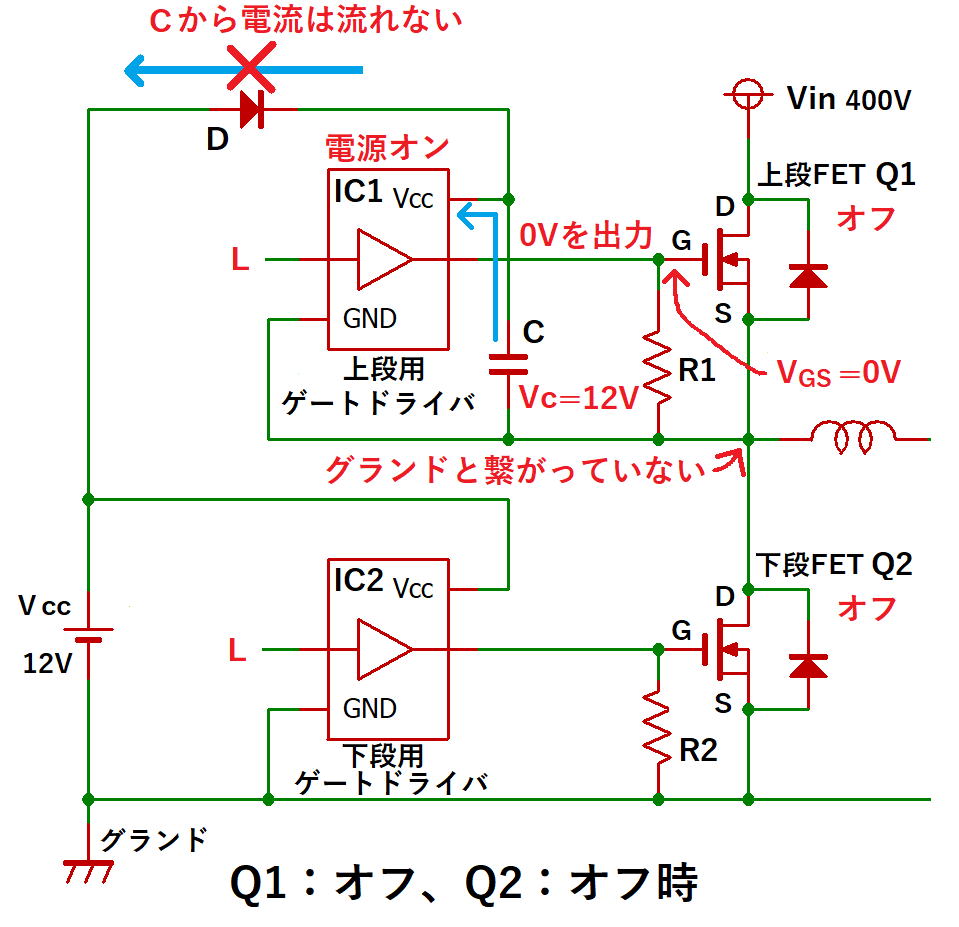

3.Q1オフ、Q2オフの時

Q2がオフすると、Q1のソース(S)は再びグランドから切り離されます。

これによって、電源VccからIC1に電流が流れなくなるので、

電源Vccからの電源供給は停止しますが、

代わりに12Vに充電されたCからの放電電流によって

IC1に電源が供給されます。

また、この時、ダイオードDがあるので、Cからの電流はVccには流れません。

Cの電圧は放電により、徐々に低下していきますが、

IC1の消費電流は小さく、しかも非常に短い期間であるため、

ここでは12Vのままとします。

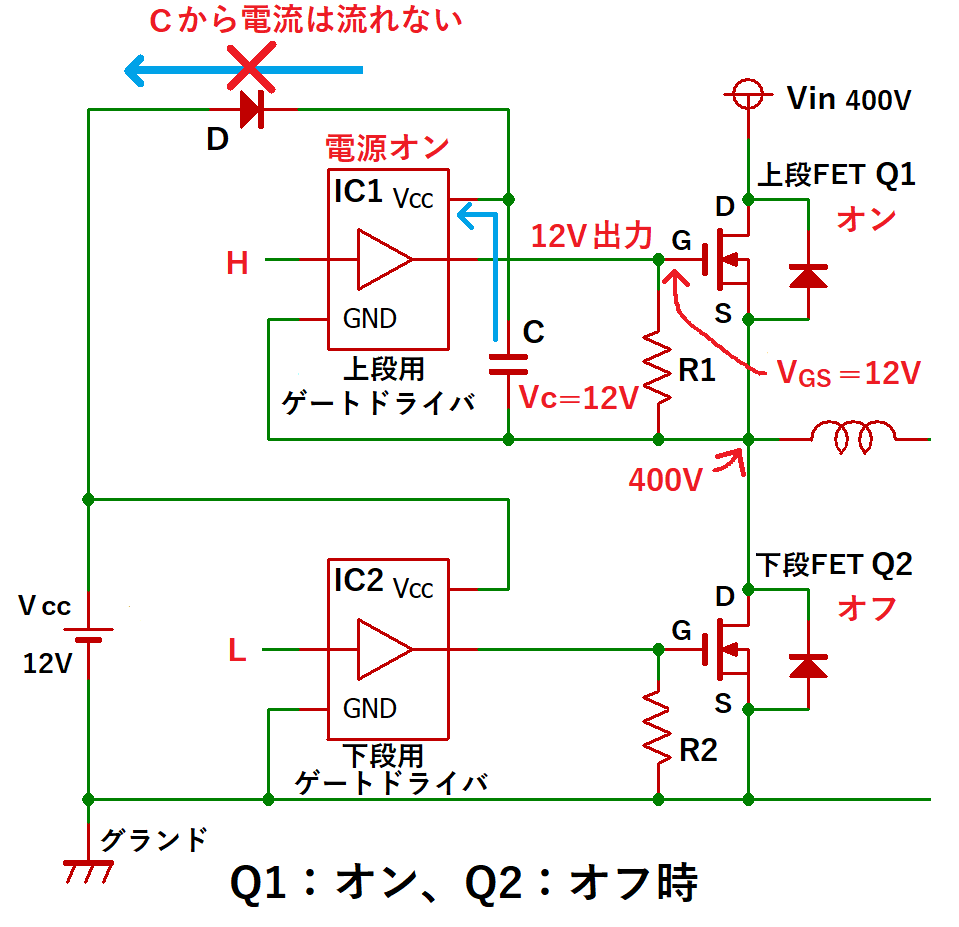

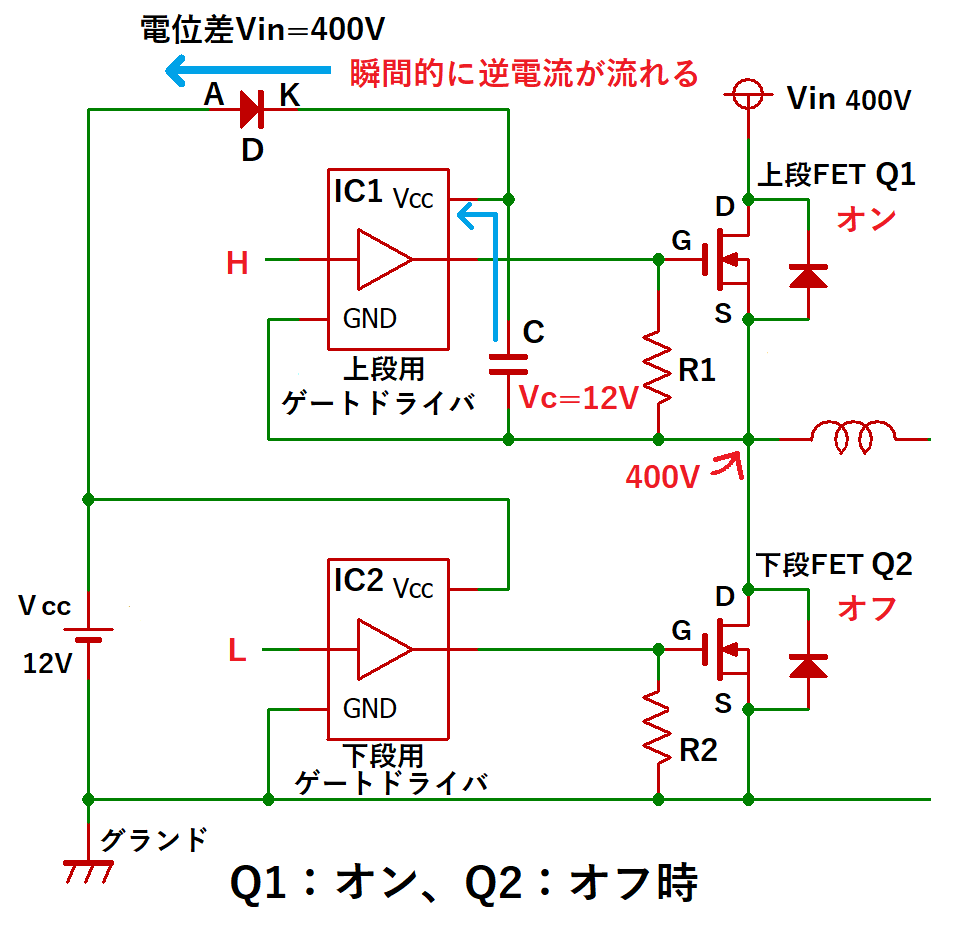

4.Q1オン、Q2オフの時

IC1には12Vが供給されているため、

入力信号がHになったら、IC1はゲート信号をHにして、Q1をオンします。

この時、Q1のソース(S)は400Vになります。

これによって、グランドを基準にした時のCの電圧は12V+400Vに上昇します。

しかし、IC1のGNDピンはQ1のソースに接続されているので、

IC1に印加される電源電圧は12Vのままです。

従って、3.と同じく、CからIC1に12Vが供給されます。

Cの電圧は放電により低下していきますが、

IC1の最低動作電圧より高いうちは問題ありません。

一方、電源Vccはグランドに接続されているので、

ダイオードDのカソード(K)~アノード(A)間には400Vが加わります。

このため、Dの耐圧は余裕をとって600V以上にする必要があります。

その後、Q1、Q2共にオフになると、3.の動作となり、

その次の、Q1:オフ、Q2:オンでは、2.の動作となって、再びCが充電されます。

ブートストラップ回路のメリット、デメリット

<メリット>

・コストが高いPch FETや、絶縁型電源を使わずに、

コンデンサとダイオードによる簡単な構成で上段FETに電源供給できる

<デメリット>

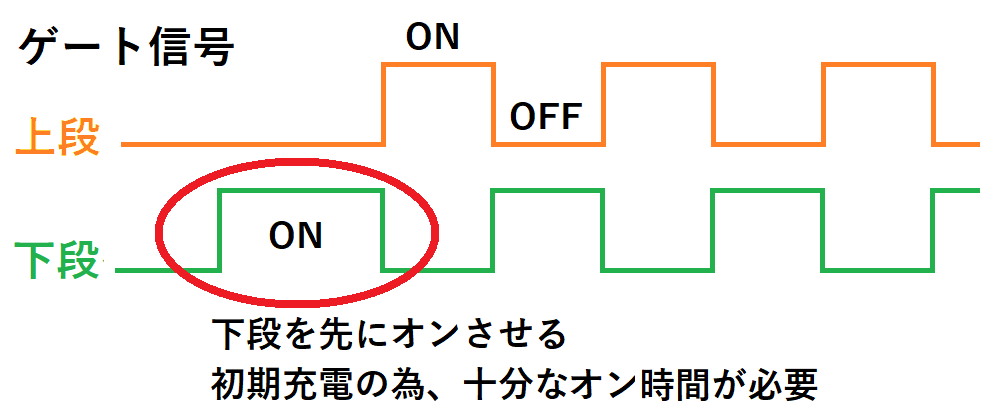

・起動時は下段FETをオンさせて、Cを充電する必要がある

これは、最初はCが充電されておらず、

上段用ゲートドライバに電源供給できない為、

FETをオンできないからです。

このため、初めは必ず、Cが充電完了するまで

下段FETをONさせる必要があります。

・PWM制御の場合、ON DUTYの上限に制限がかかる

ON DUTYはスイッチング周期に対する上段FETのON時間の割合です。

PWM制御の場合、出力電流を増やす時はON DUTYを大きくします。

しかし、ON DUTYが大きくなり過ぎると、

Cの充電時間が不足する事でC電圧の低下が大きくなり、

上段用ゲートドライバへの電源供給が維持できなくなります。

このため、ON DUTYに上限を設ける必要があり、

それによって、出力が制限されてしまいます。

また、ON DUTYが一定の周波数制御でも同様の問題が発生します。

LLC電流共振コンバータの場合、ON DUTYは50%固定で、

出力電流を増やす時は周波数を低くします。

この時、周波数が低くなり過ぎると、

Cの放電時間が長くなる事でC電圧の低下が大きくなり、

上段用ゲートドライバへの電源供給が維持できなくなります。

ブートストラップ・ダイオードの選定

ブートストラップ回路のダイオードには、

ファストリカバリダイオードを使います。

その理由は、逆回復時間が短いためです。

本来、ダイオードはカソード(K)からアノード(A)に電流を流しませんが、

順電流が流れている時に、急に逆電圧を印加すると

短い時間ですが、逆方向(K→A)に電流が流れます。

この時間を、ダイオードの逆回復時間Trrと言います。

ブートストラップ回路では、

スイッチング周期毎に逆電圧が印加されるため、

その都度、逆電流が流れてしまいます。

この時、K~A間の電圧はVinとなるので、

逆電流Iが流れた時のダイオードの損失は

P=Vin × I

となります。

入力電圧Vinが高電圧だと、損失が無視できなくなります。

この損失を低減させるため、逆回復時間が短いものを選定する必要があるのです。

但し、逆回復時間が短いと、順方向電圧VFが大きくなる特徴があるため、

コンデンサCの充電電圧が低くなってしまいます。

コンデンサC電圧=VccーVF

このため、VF分下がっても、ゲートドライバの最低電源電圧を下回らないようにします。

また、ダイオードの耐圧はVinに比べ、十分高いものにします。

(例としてVin=400Vの場合は、耐圧600V以上を選定)

ブートストラップ・コンデンサの選定

使用するコンデンサはスイッチング周波数で充放電が行われるため、

高周波特性が良いSMDタイプの積層セラミックコンデンサ(MLCC)を使用します。

(以下、セラコンと称します)

必要な容量値の求め方を説明します。

セラコンに充電された電圧Vcが、

ゲートドライバへの電源供給によって電圧がΔVcだけ低下した場合、

セラコンが失う電荷量Qbsは

Qbs=C×ΔVc

となります。

このQbsは、FETをオンするのに必要な電荷量と、

ゲートドライバに必要な電荷量(消費電流×電流が流れる時間)の合計なので、

以下の式が成立します。

Qbs=Qg + Icc × Ton

Qg:ゲート入力電荷量

FETがオンするのに必要な電荷量で、データシートに記載されています。

Icc:ゲートドライバの消費電流

ゲート出力からの電流を除く、IC自体の動作に必要な分です。

メーカーによって表現は違いますが、Quiescent Current(静止電流)等と記載されています。

Ton:上段FETのON時間

ON DUTY(D)と、スイッチング周波数(f)から

Ton=D/f

となります。

以下の回路の場合を例として、容量を求めます。

ゲートドライバ:アナログデバイセズ製 ADuM4121

FET :東芝製 TK9A60D

スイッチング周波数:100kHz

ゲート電圧 :12V

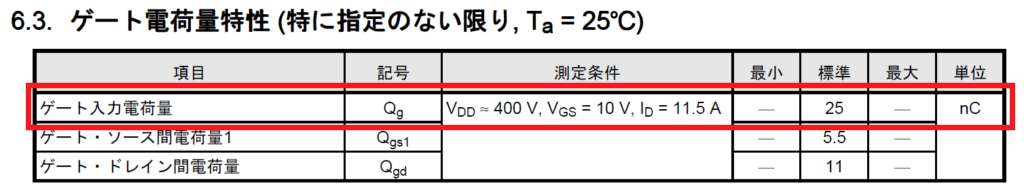

ゲート入力電荷量QgはFETのデータシートを見ると25nCとありますが、

これはVGS=10Vにするのに必要な電荷量です。

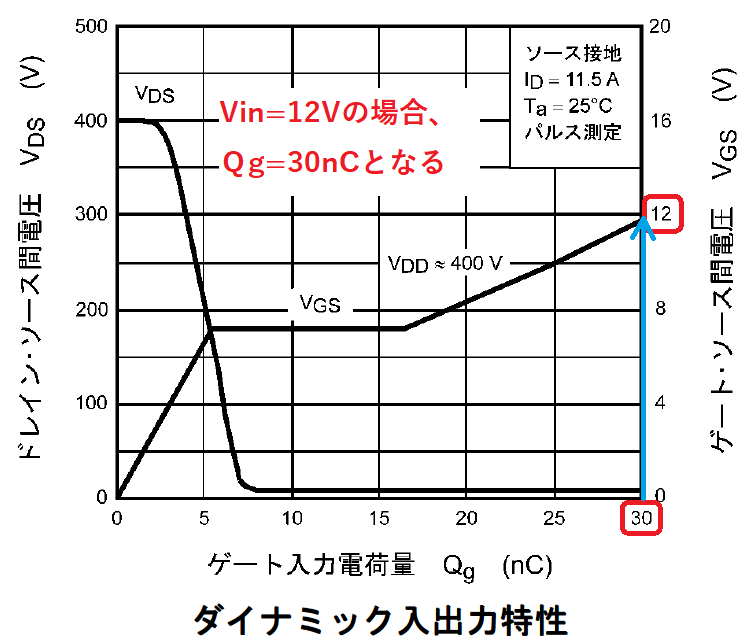

VGS=12Vの場合は、QgーVGSグラフ(ダイナミック入出力特性)を見ると、

Qg=30nC

であることがわかります。

ゲートドライバの消費電流Iccですが、

ADuM4121は入力と出力が絶縁されているタイプであり、

Cから電源供給するのは出力側であることから、

出力側 静止電流2.7mAが該当します。

上段FETのON時間Tonについては、

ここでは、ON DUTYを50%として計算してみます。

Ton=D/f=0.5/100kHz=5us

よって

Qbs= Qg + Icc × Ton

=30nC+2.7mA×5us

=30nC+13.5nC=43.5nC

C放電時の電圧降下分ΔVcを0.1Vに抑える場合、

Qbs=C×ΔVc より

C=Qbs/ΔVc

=43.5nC/0.1V=0.435uF

となり、これよりも大きい容量にする必要があるので、

セラコンの一般的な容量ラインナップであるE12系列から

0.47uFを選択します。

セラコンの耐圧については、電源電圧Vccが印加されるので、

それより高い電圧にするのは当然なのですが、

それ以外に、DC バイアス特性を考慮する必要があります。

DC バイアス特性とは印加されるDC 電圧によって容量が変化する特性のことで、

高誘電率型のセラコンの場合、一般的に 電圧が上昇すると容量が減少します。

温度補償型ならDC電圧が高くなっても容量が殆ど変化しませんが、

ブートストラップで使用する0.1uF以上の高容量では殆どありません。

この減少の度合いは、セラコンの耐圧が低く、チップサイズが小さい程顕著になります。

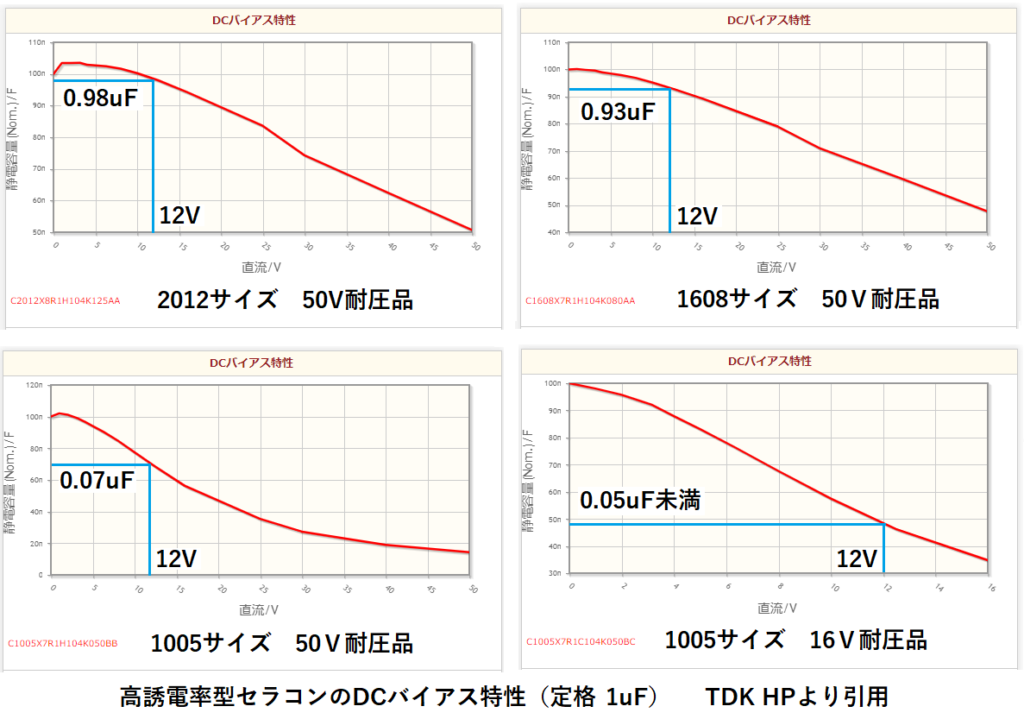

定格容量1uFの場合、DC12V印加時の容量を見ると、

2012サイズの50V耐圧品では0.98uFですが、1608サイズで0.93uF、

1005サイズだと0.7uFまで低下します。

更に16V耐圧品になると、0.5uFとなり、半分以下となります。

このため、できるだけ耐圧が高く、チップサイズの大きいものを選びます。

ブートストラップ・制限抵抗の選定

先程の動作説明では抵抗はありませんでしたが、

実際の回路では電流制限抵抗が必要な場合があります。

その理由は、2つあります。

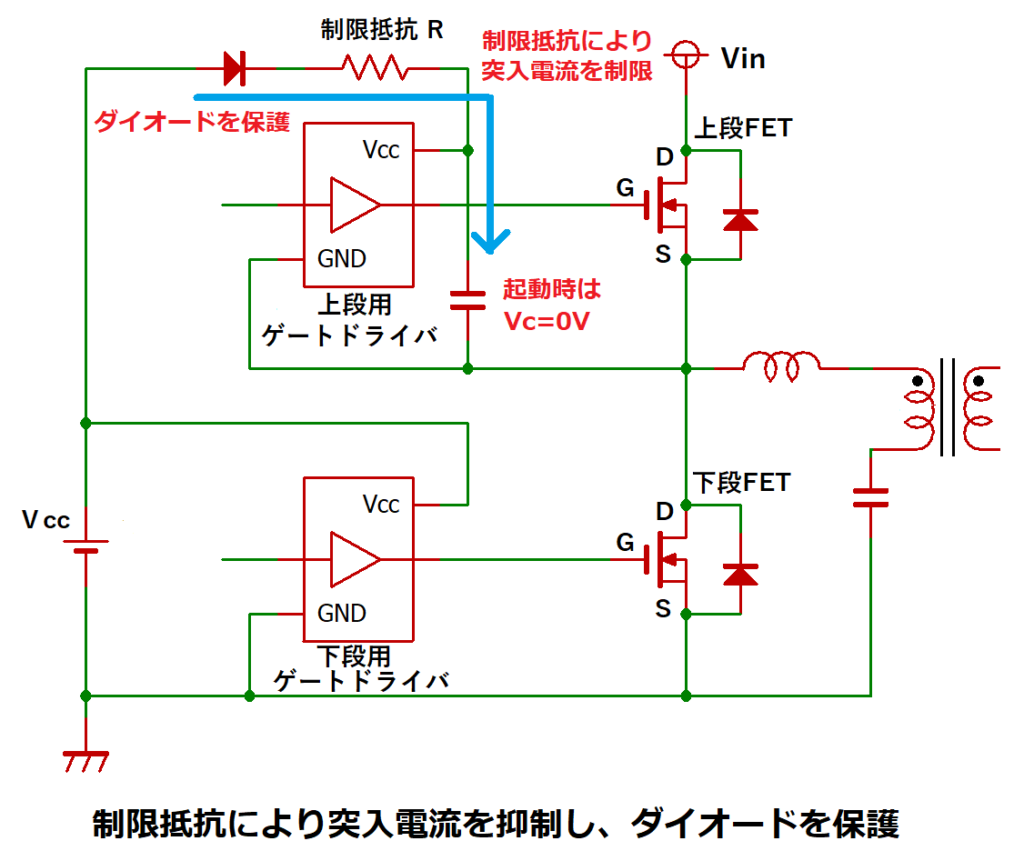

1.起動時にダイオードの最大電流を超えないようにするため

起動時はコンデンサCが充電されてない(つまり、Vcがゼロ)為、

下段FETがオンすると、瞬間的に大きな電流がダイオードに流れます。

この電流がダイオードの最大定格(サージ順電流)を超えないように

抵抗をつけて突入電流を制限します。

ダイオードのサージ順電流 > Vcc/R

但し、Rをつけることで、充電電流が制限されるため、

コンデンサの充電時間が長くなります。

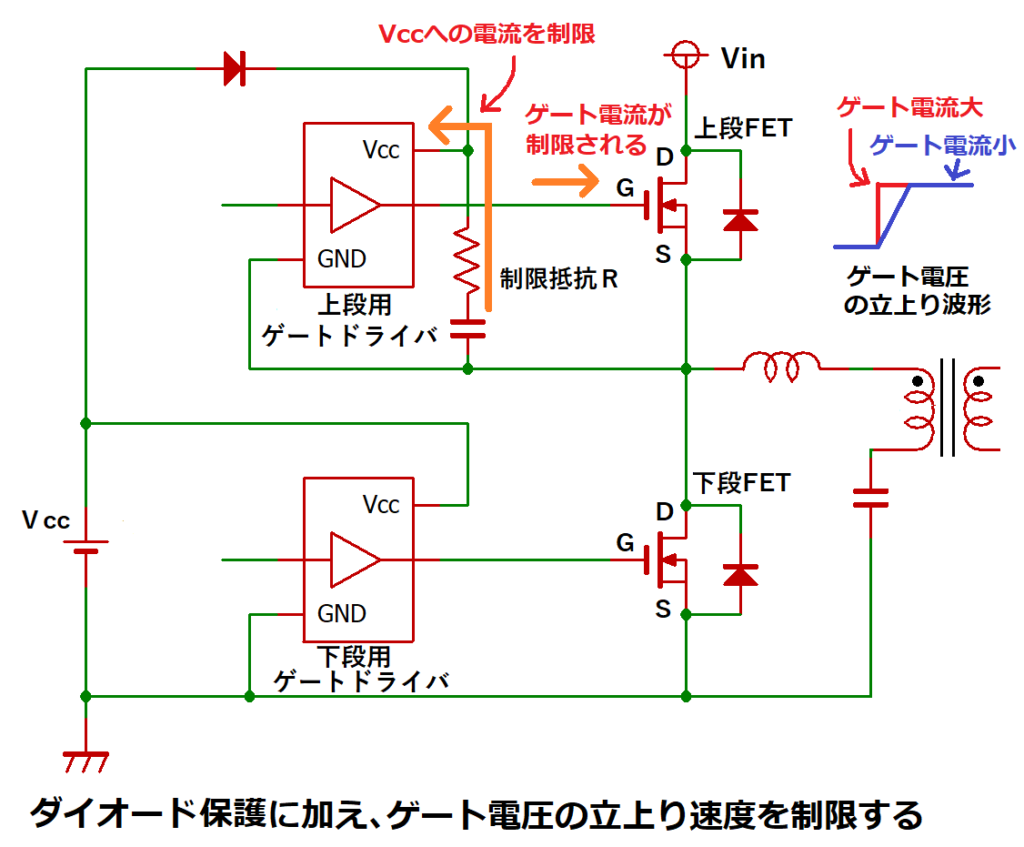

2.FETのゲート電圧の立上りを制限するため

ゲート電圧の立上りが急過ぎるとFETがオンする速度が速くなるため、

スイッチングノイズが大きくなります。

この場合、ゲートに入力する電流を減らせば、

ゲート端子の充電時間が長くなり、ゲート電圧の立上りを遅くする事ができます。

ゲート電流を減らす方法としては、ゲート抵抗をつけるのが一般的ですが、

ゲートドライバとFETが一体型のデバイスではそれができません。

このため、抵抗Rをつけることで、ゲートドライバへの供給電流が制限され、

その結果、ゲートドライバからのゲート電流を減らすことができます。

先程の回路図(突入電流抑制)と比較して、Rの位置が違っています。

この回路ではダイオードの突入電流抑制に加え、

Cから電源ピンへの供給電流を制限しています。

これによって、ドライバからのゲート電流も制限されるので、

ゲート電圧の立上りを遅くすることでスイッチングノイズを低減できます。

但し、ゲート電圧の立上りを遅くすると、ターンオン損失が大きくなります。

以上より、抵抗をつける事によるデメリットもあることから、

一般的に抵抗値は数Ω程度です。

ツェナーダイオードによる過電圧保護

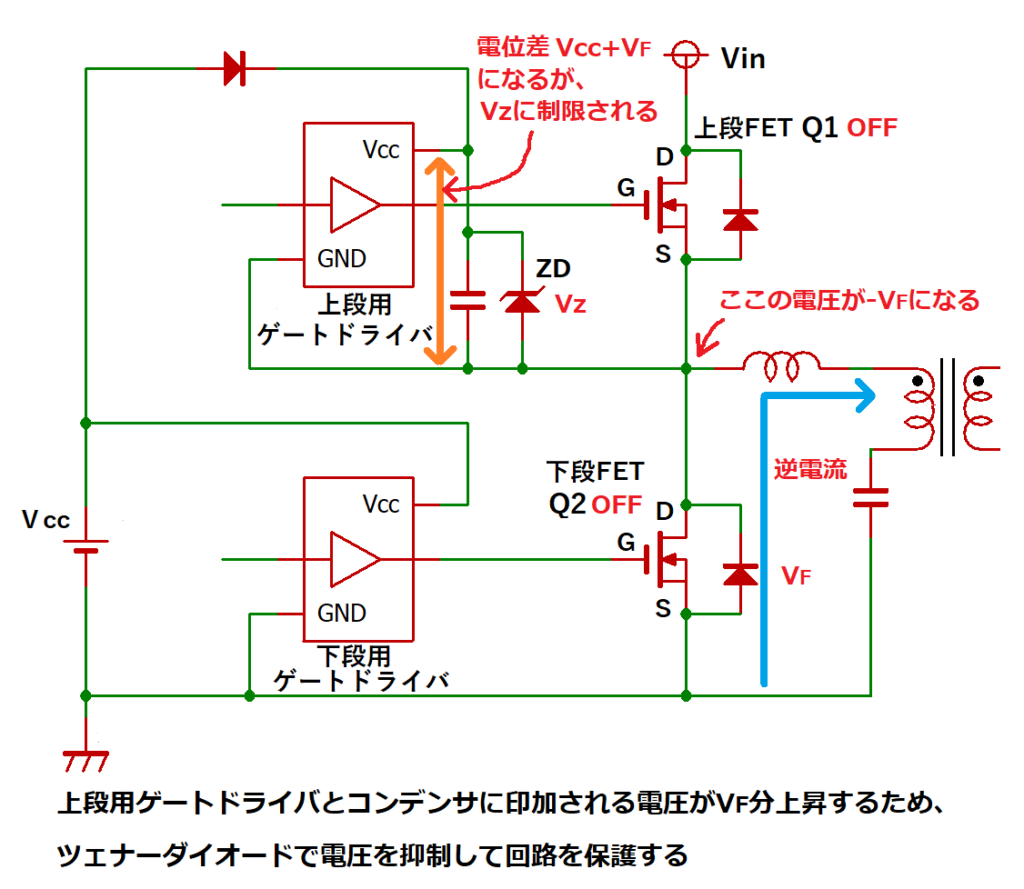

上下のFETが共にOFFであるデットタイムの時、

上段用ゲートドライバに印加される電源電圧が上昇します。

その理由ですが、

Q1:オン、Q2:オフの状態から、Q1がオフするとQ1からの電流は停止しますが、

ハーフブリッジの出力に接続されている誘導性負荷(コイルやモータ等)の働きにより、

電流を維持しようとするので、Q2のボディダイオード経由で逆電流が流れます。

Q2に逆電流が流れることで、ボディダイオードの順方向電圧VF分だけ

グランドよりQ2のドレイン(D)電圧が低くなります。

これは、上段用ゲートドライバのGNDピンを基準にした時、

電源ピンVccに印加される電圧がVF分高くなることを意味します。

上段用ゲートドライバ電源電圧=Vcc+VF

FETによってはVFが2V近くあるため、

ゲートドライバ及びコンデンサの最大定格電圧を超えないように

ツェナーダイオードによる電圧クランプが必要な場合があります。

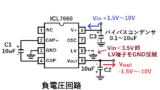

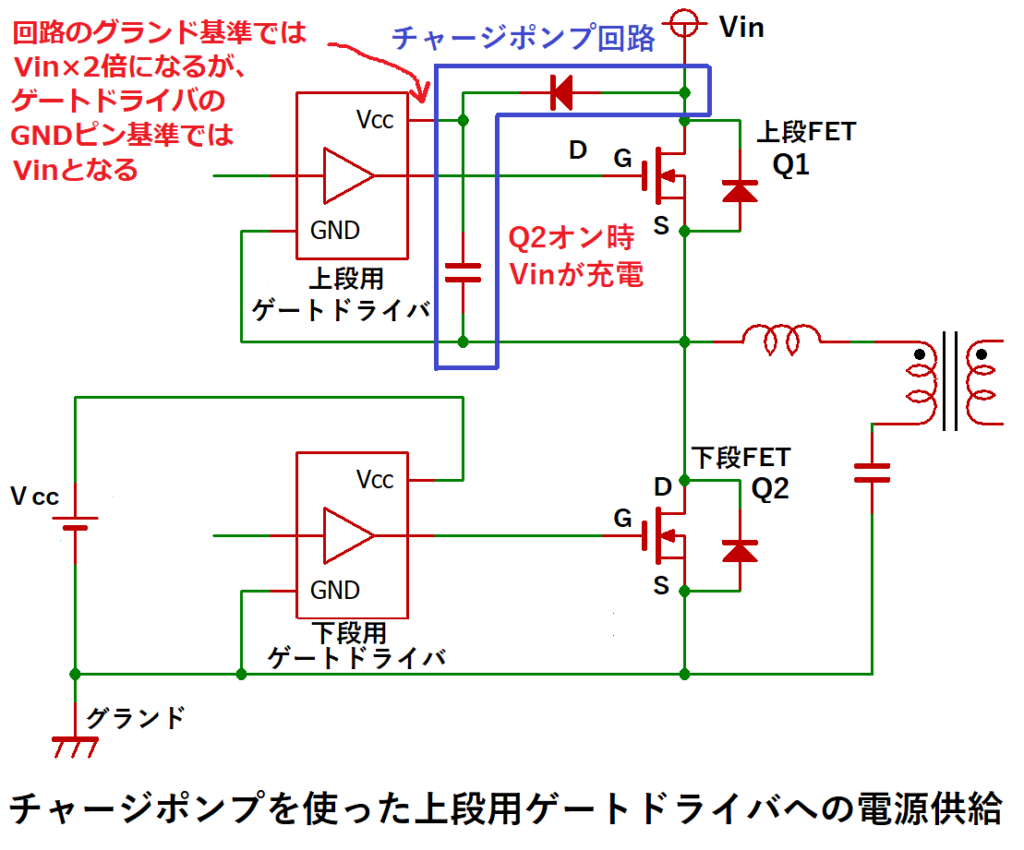

チャージポンプを使ったハイサイド電源供給方法

ブートストラップと同じく、

コンデンサとダイオードを使った電源供給回路に

チャージポンプがあります。

チャージポンプは、その名の通り、

コンデンサに充電(チャージ)した電圧を使って、

出力を2倍に昇圧(ポンプ)することができます。

このチャージポンプでも上段用ゲートドライバへの電源供給が可能です。

チャージポンプの場合、グランドから見た時のコンデンサの電圧は

入力電圧Vinの2倍になりますが、ゲートドライバにとってはVinが印加されます。

ブートストラップとの違いは、

上段用ゲートドライバには電源電圧Vccが不要な事であり、

ハーフブリッジ回路の入力電圧Vinを使って電源供給します。

但し、この方法は、入力電圧Vinがそのまま電源電圧になるため、

Vinがゲートドライバの最大定格電圧より低くないと使えません。

チャージポンプ回路については下記記事で解説しています。

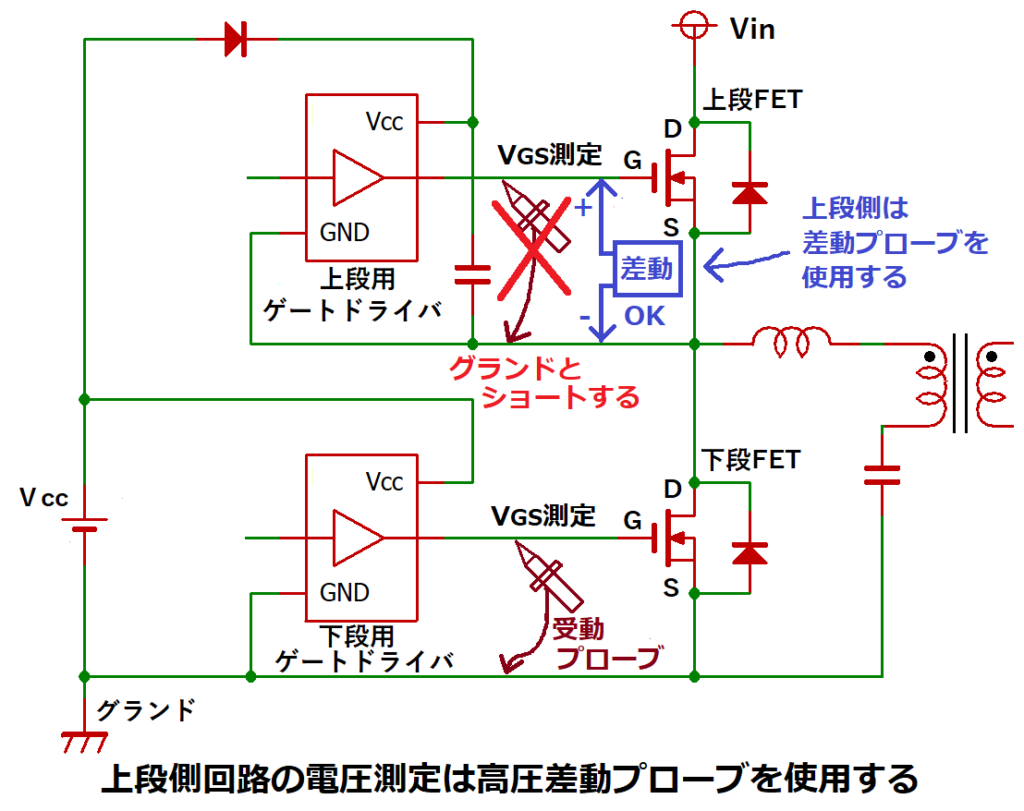

上段側の電圧測定時の注意点

上段FETのゲート信号や、ゲートドライバの電源電圧を測定する際、

標準(受動)プローブを使うとFETが故障します。

理由は、他のプローブのグランドが回路グランドに接続されていると、

オシロスコープを経由して、上段FETのソースがグランドにショートされてしまいます。

この状態で上段FETがオンすると短絡電流が流れてしまい、

まず、上段FETがショート故障し、

その状態で下段FETがオンすると下段も短絡電流で故障します。

このため、上段側は高電圧差動プローブを使用します。

差動プローブのグランドを上段FETのソースに接続しても、

回路のグランドと絶縁することができ、故障を防ぐ事ができます。

★基板の部品交換や修正で役立つ工具類を紹介しています。