この記事でわかること

・プルアップ、プルダウンをつける理由

・プルアップ、プルダウンの原理と効果

・抵抗値の決め方、計算方法(ケース別)

デジタル回路に必ず出てくるプルアップ抵抗ですが、

その抵抗値は回路によって様々です。

時には、数百Ω程度の小抵抗も使用され、

どうして、その値にしたのか疑問に思うかもしれません。

また、プルダウン抵抗においては、デジタルICだけでなく、

トランジスタやFETでも、多く使われています。

本記事では、

プルアップ・プルダウンを付ける事による効果と、

抵抗値の計算方法について、ケース別に解説します。

プルアップ・プルダウン抵抗をつける理由

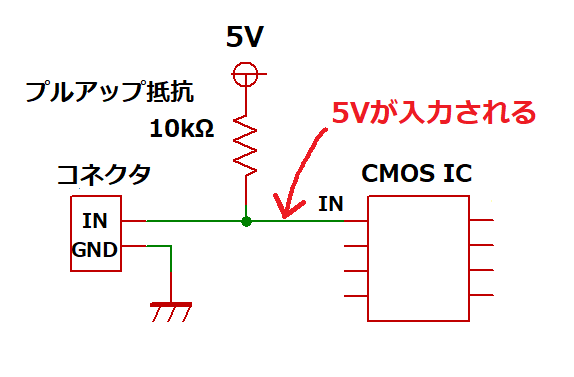

<プルアップ抵抗をつける理由>

・入力信号が無い時にHレベルに固定させたい場合

外部機器からの信号を入力する回路において、

コネクタに何も接続されていない場合、ICへの入力が不安定にならないように

プルアップ抵抗を接続して、Hレベル電圧に固定させます。

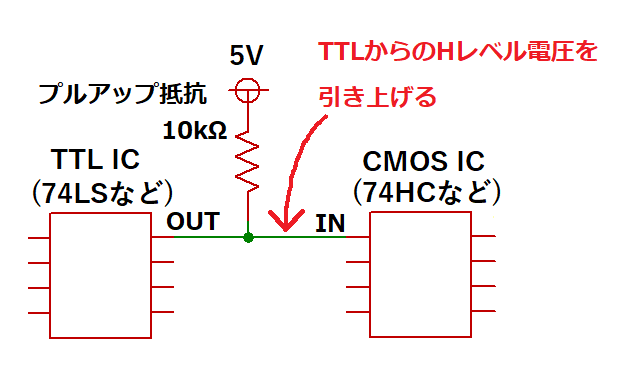

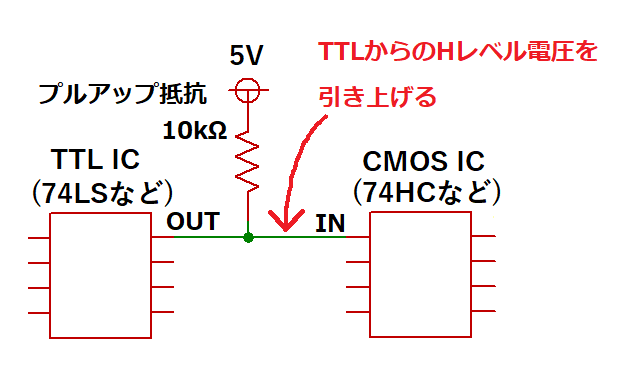

・TTL IC の出力をCMOS ICに入力する場合

TTL IC(※1)のHレベル出力電圧の最低値は2.4Vです。

しかし、5V系 CMOS ICがHレベルと認識できる電圧が3.5V以上なので、

TTL ICの出力をそのままCMOS ICに入力しても、Hレベルを認識できません。

プルアップ抵抗を接続することで、CMOS ICへの入力電圧を上昇させ、

Hレベルと認識させることができます。

※1:TTL(Transistor-Transistor Logic)

バイポーラトランジスタで構成されたロジックICです。

現在はCMOS ICが主流であり、あまり利用されていませんが、

その入出力電圧条件であるTTLレベルは制御機器で使われています

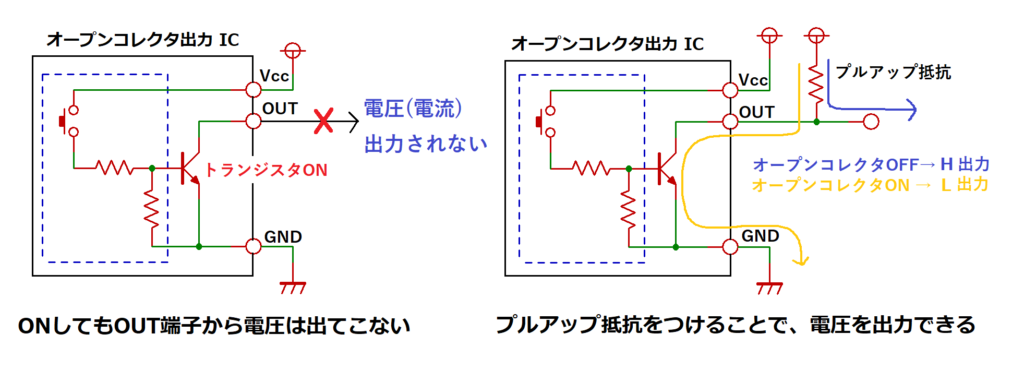

・オープンコレクタ出力を入力する場合

オープンコレクタやオープンドレイン出力を持つICは、

出力端子に何もつながっていない状態(オープン)なので、

このままでは電圧を出力できません。

出力にプルアップ抵抗をつけることで、

出力がOFF時はH電圧、ON時はL電圧を出力できます。

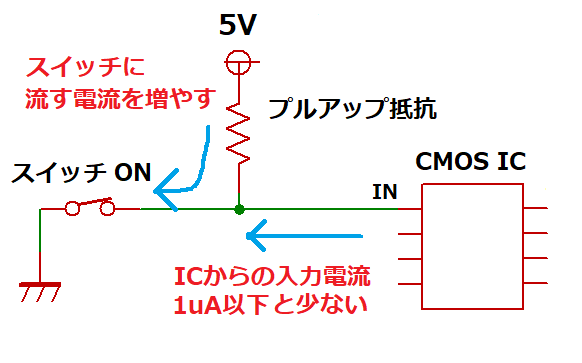

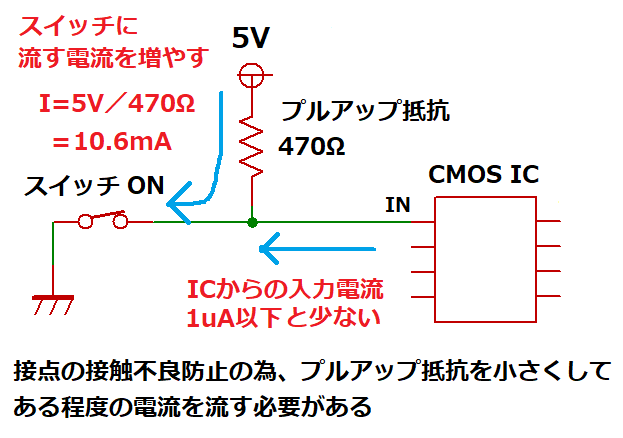

・接点出力を持つ機器に流れる電流を増やしたい場合

スイッチやリレー等の接点出力をICに入力する場合、

接点に流れる電流が小さ過ぎると、

開閉を繰り返すうちに酸化皮膜が生成されて接触不良となります。

このため、ある程度の電流(10mA以上)を流してアーク放電を起こして、

酸化被膜を破壊させる必要があります。

数百Ω程度のプルアップ抵抗をつけることで、

接点に流す電流を増やすことができます。

<プルダウン抵抗をつける理由>

・入力信号が無い時にLレベルに固定させたい場合

プルアップ抵抗と同様、ICへの入力が不安定にならないように

プルダウン抵抗を接続して、Lレベル電圧に固定させます。

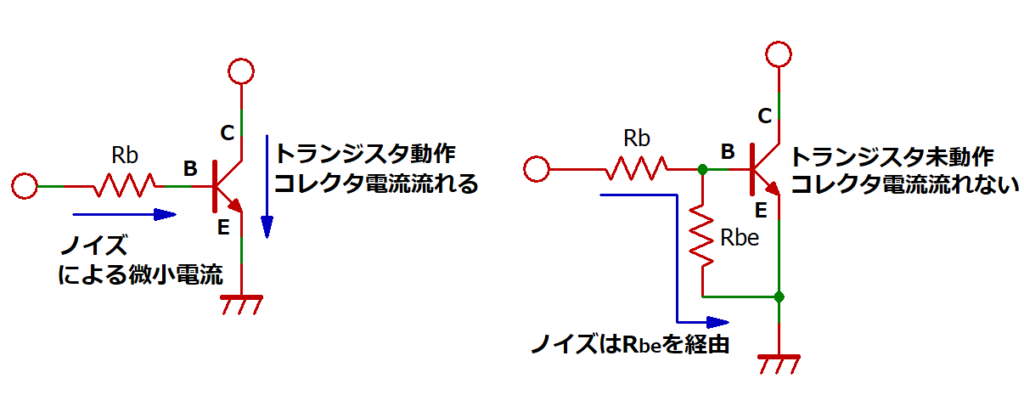

・トランジスタやFETの誤動作防止

トランジスタのベース・エミッタ間や、

FETのゲート・ソース間に接続することで、

信号が入力されない場合や、ノイズの流入によって、

誤動作しないようにします。

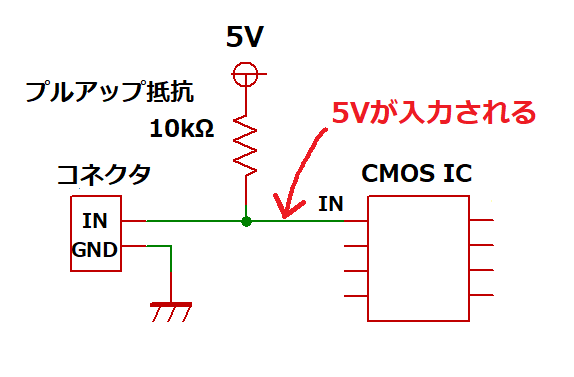

プルアップ抵抗の原理と効果

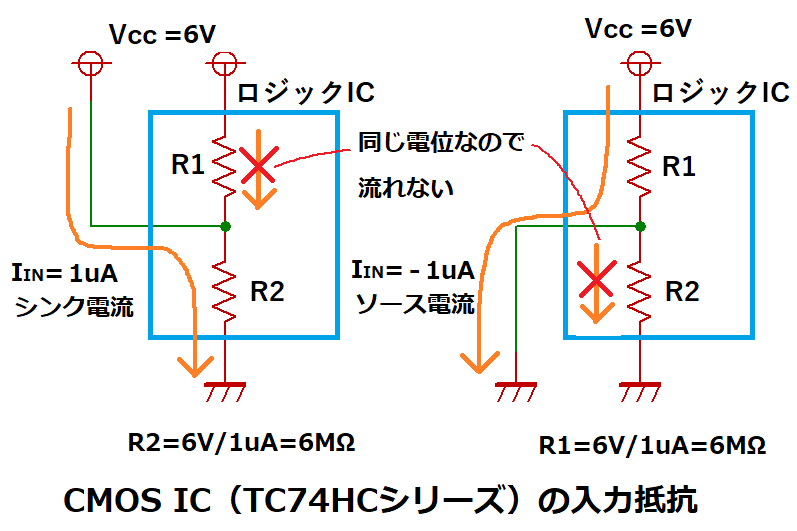

図のように、5V電源にプルアップ抵抗10kΩをつなげると、

ICの入力には5Vが入力されます。

抵抗を経由しているのに入力電圧が5Vになる理由は、

CMOS ICの入力抵抗が非常に大きいからです。

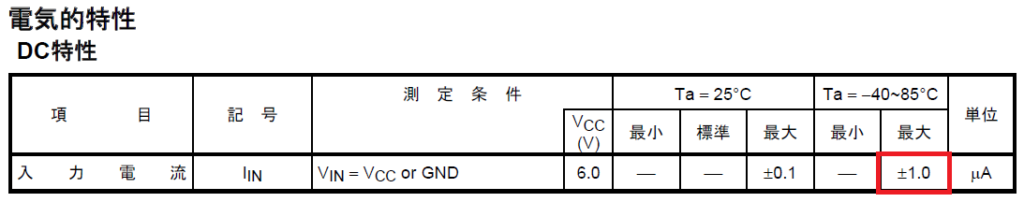

例えば、東芝製 CMOS ロジックIC TC74HC04のデータシートを見ると、

入力電流IIN=±1uAです。

ここで、±符号は電流の方向を表しています。

+はICに入る方向(シンク電流)

ーはICから出る方向(ソース電流)

<シンク電流とソース電流>

キッチンの流しをシンクといいますが、

水が流れ込む部分、つまりICに流れ込むのがシンク電流です。

ソースは源泉という意味なので、

水が湧き出る部分、つまりICから流れ出すのがソース電流です。

ロジックICの入力回路は図のように

内部等価抵抗R1、R2で置き換えることができます。

入力電流1uAは記載されている条件から、

VIN=Vcc=6Vの時にICに流れ込むシンク電流なので、

この時の入力抵抗R2は

R2=Vcc/IIN=6V/1uA=6MΩ

となります。

入力電流-1uAについても同様に、

VIN=GND=0Vの時にICから流れ出すソース電流です。

この時の入力抵抗R1は

R1=Vcc/IIN=6V/1uA=6MΩ

となります。

ここで、プルアップ抵抗10kΩを接続した場合、

10kΩと6MΩの並列抵抗Rmixは

Rmix=10kΩ×6MΩ/(10kΩ+6MΩ)

=9.98kΩ

となります。

5VがRmix=9.98kΩとR2=6MΩで分圧されるので、

入力電圧Vinは

Vin=5V×9.98kΩ/(9.98kΩ+6MΩ)

=4.99V

となり、ほぼ5Vが入力されます。

ここでは、プルアップ抵抗を10kΩとしましたが、

Hレベルに固定するだけなら、入力抵抗の6MΩより十分小さければ良いのですが、

外部から信号を入力してLレベルにするためには、抵抗値に更に制約が発生します。

次に、入力する信号の種類に応じたプルアップ抵抗値の決め方について説明します。

プルアップ抵抗値の決め方(CMOS 出力の場合)

入力機器がCMOS出力の場合、

プルアップ抵抗値は以下になります。

ここでは、入力機器から信号を出力するICを前段IC、

その信号を入力するICを後段ICと称することにします。

・プルアップ抵抗の上限値:Rmax

(VccーVIHmin)/ IINmax > Rmax

VIHmin:後段ICの最小Hレベル入力電圧

IINmax:後段ICの最大入力電流

・プルアップ抵抗の下限値:Rmin

(VccーVOLmax)/ IOL< Rmin

VOLmax:前段ICの最大Lレベル出力電圧

IOL :前段ICのLレベル出力電流(VOLmax出力時)

上記の式になる理由を以下で説明します。

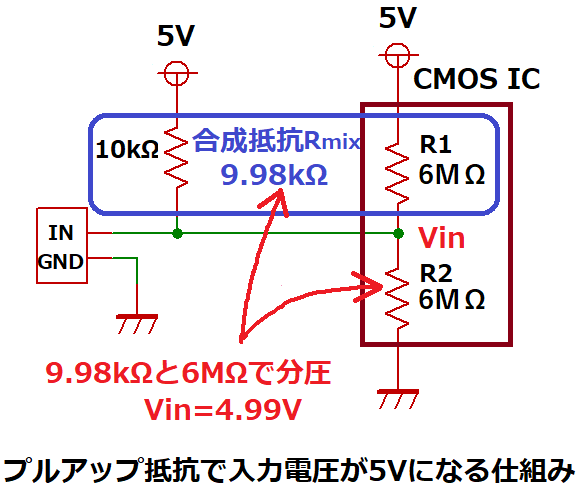

<上限値の決め方>

まず、前段ICが未接続で電圧が入力されなくても、

プルアップ抵抗だけで、Hレベルと認識できるようにする必要があります。

プルアップ抵抗を後段ICに接続した時、

ICに入力電流が流れるので、

プルアップ抵抗による電圧降下が発生します。

この電圧降下によって、

後段ICの入力電圧が最小Hレベル入力電圧VIHminより低くなると、

Hと認識できなくなります。

このため、プルアップ抵抗による電圧降下があっても、

VIHminより高くなるようにします。

Vccー(Rmax × IINmax)>VIHmin

変形すると、先ほどの式になります。

(VccーVIHmin)/ IINmax>Rmax

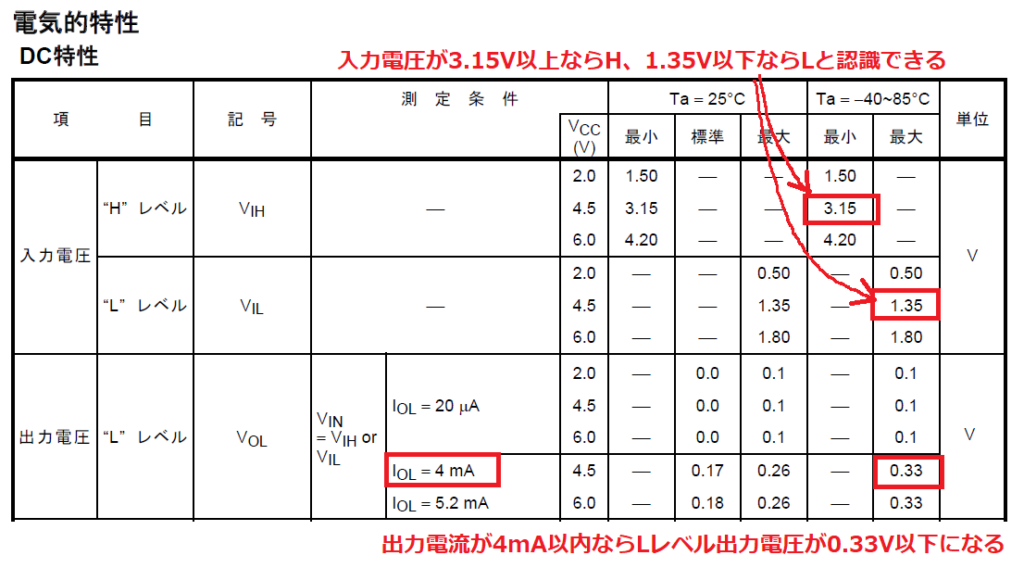

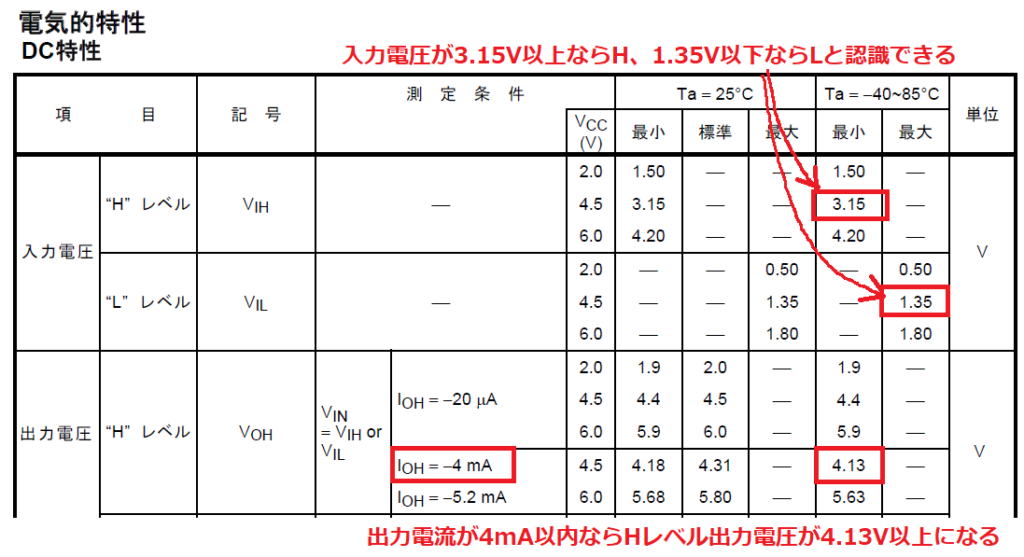

TC74HC04の場合、データシートより、

VIHmin=3.15V、IINmax=1uAなので、

(5Vー3.15V)/1uA=1.85MΩ>Rmax

となり、プルアップ抵抗は1.85MΩ以下にする必要があります。

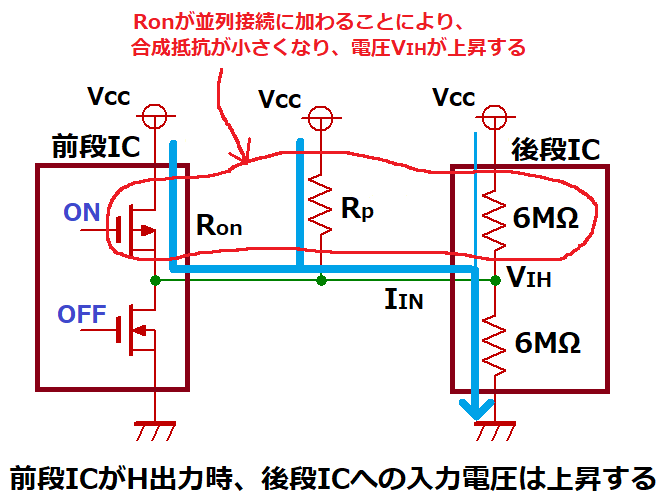

ちなみに、前段ICを接続して、H出力させた場合は、

前段ICの上段FETのON抵抗とプルアップ抵抗の並列接続となるので、

抵抗値が小さくなり、後段ICへの入力電圧は上昇します。

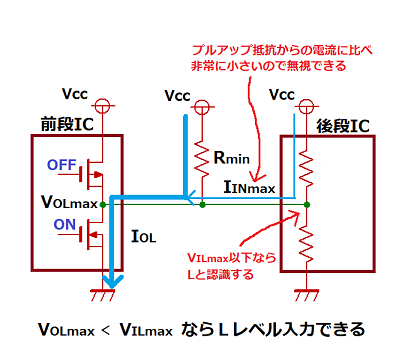

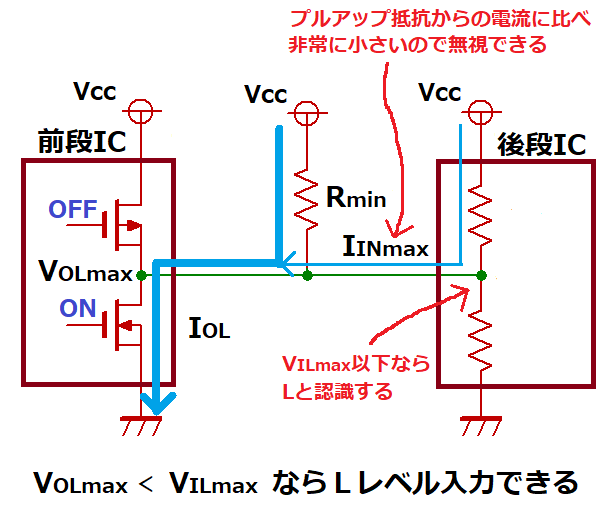

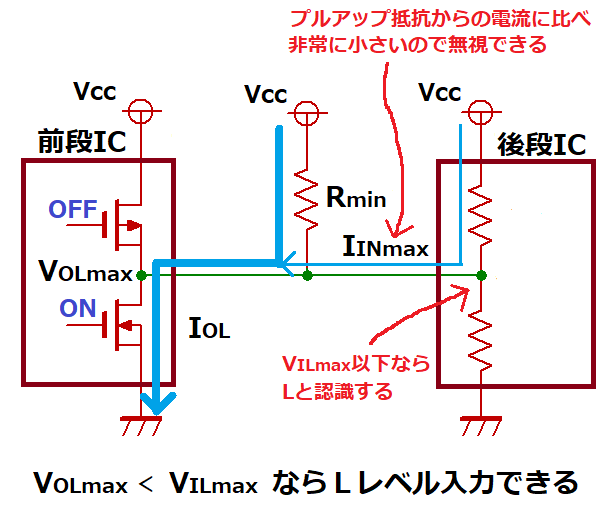

<下限値の決め方>

後段ICにL信号を入力するには、

前段ICの出力電圧をLレベルまで下げる必要があります。

しかし、プルアップ抵抗が小さすぎると、

前段ICに流れ込む電流が大きすぎて、

出力電圧が上昇し、後段ICでLと認識できなくなります。

前段ICのデータシートを見ると、

最大Lレベル出力電圧VOLmaxと、

その時に流れ込む電流IOLが規定されています。

つまり、前段ICに流れる電流がIOL以内なら、

出力電圧はVOLmax以下であることを意味します。

従って、

前段ICのLレベル出力電圧VOLmax<後段ICのLレベル入力電圧VIHmax

ならば、後段ICでLと認識できます。

このため、プルアップ抵抗に流れる電流を

IOLよりも小さくなるようにします。

(VccーVOLmax)/ Rmin< IOL

厳密には、後段ICからも電流が流れてきますが、

最大でも1uAであり、プルアップ抵抗から流れる電流(mAレベル)

に比べて非常に小さいため、無視できます。

変形すると、先ほどの式になります。

(VccーVOLmax)/ IOL< Rmin

TC74HC04の場合、データシートより、

VOLmax=0.33Vで、その時のIOLは4mAなので、

(5Vー0.33V)/4mA=1.16kΩ

となり、プルアップ抵抗は1.16kΩ以上にする必要があります。

以上の結果から、

1.16kΩ<プルアップ抵抗<1.85MΩ

となります。

抵抗値の範囲がかなり広いですが、

プルアップ抵抗が大きいとL→H時の立上り時間が長くなり、

立下り時間との差が広がるので、注意が必要です。

<プルアップ抵抗が大きいと立上り時間が長くなる理由>

CMOS ICの入力はコンデンサに置き換えることができ、

プルアップからの電流が小さいと、コンデンサの充電に時間がかかるため、立上り時間が長くなります。

L出力時はプルアップからの電流は前段ICに流れるので、立下り時間には影響を与えません。

実際には、ノイズが入ってもHレベルを維持できるように

電圧を高くするため、できるだけ抵抗値を小さくします。

このため、一般的には4.7kΩや10kΩが使われています。

プルアップ抵抗値の決め方(TTL 出力の場合)

記事の冒頭で説明したように、TTL ICからのHレベル出力電圧(2.4V)が

CMOS ICがHレベルと認識できる電圧(3.5V)より低いため、

プルアップ抵抗でHレベル電圧を上げる必要があります。

プルアップをつけると、なぜ電圧が上がるかについて説明します。

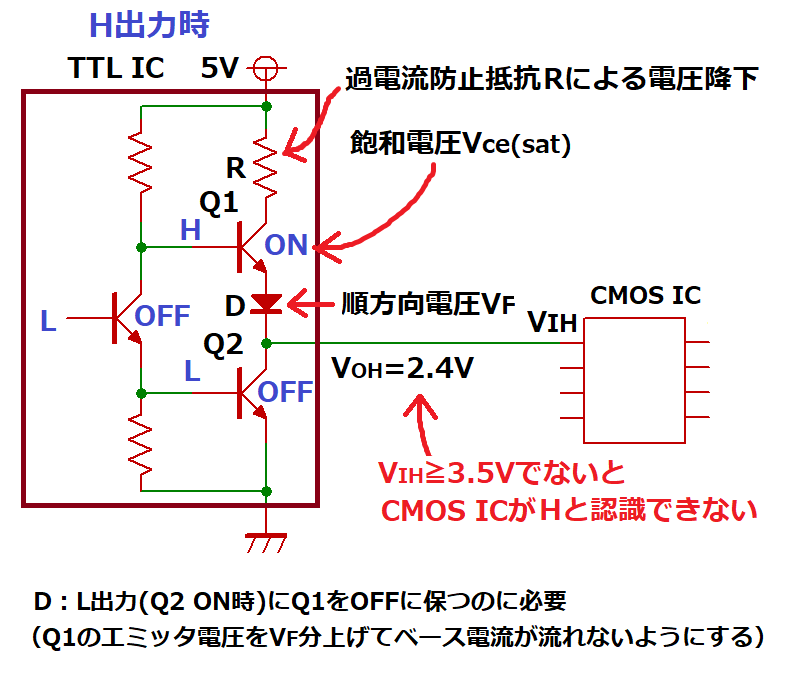

TTL出力は図のようにトランジスタ2段構成になっていて、

H出力時はQ1をON、L出力時はQ2をONしています。

プルアップ抵抗が無い場合、TTLがH出力すると、

Q1のコレクタ・エミッタ間飽和電圧VCE(sat)と、

回路図中の抵抗RとダイオードDによる電圧降下があるため、

Hレベル出力電圧VOHは最大2.4Vまで低下します。

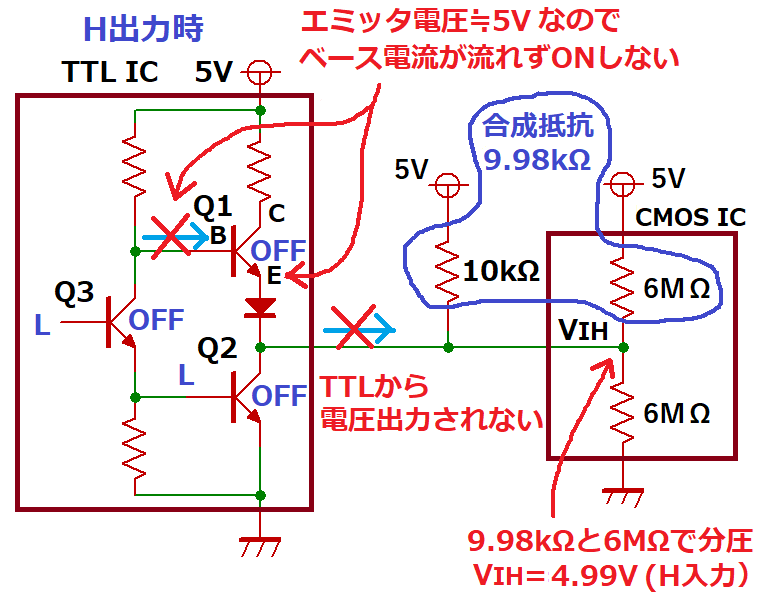

次に、CMOS ICの入力にプルアップ10kΩをつけた場合、

入力電圧が4.99Vになることは先で説明した通りです。

プルアップされたCMOS ICの入力にTTL ICの出力を接続した場合、

TTLがH出力時、Q2はOFFなので、出力端子には4.99Vが印加されます。

そうなると、Q1のエミッタ電圧は、ほぼ5Vになり、

Q3がOFFしても、ベース~エミッタ間の電位差が無いため、

ベース電流は流れず、Q1はOFFのままです。

これにより、Q1、Q2ともOFFになるので、

TTL ICからは電圧が出力されなくなります。

従って、プルアップ抵抗を経由した4.99VがCMOS ICに入力されます。

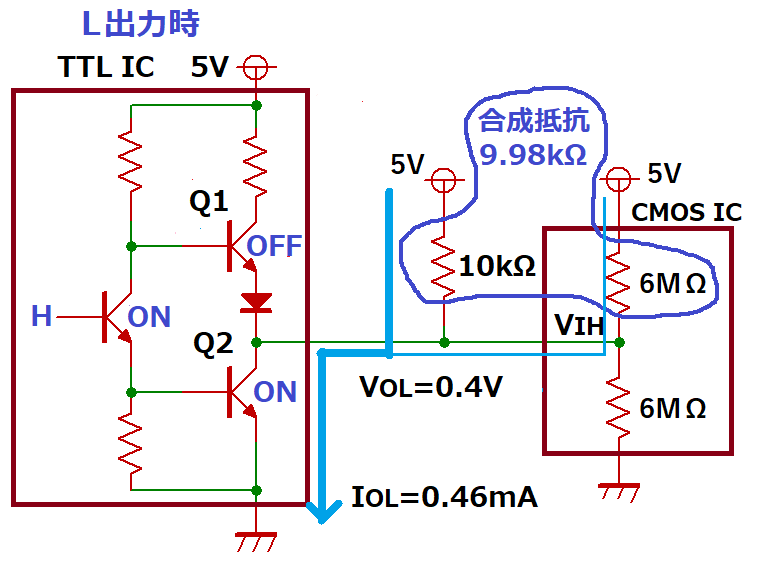

L出力時はQ2がONするので、

出力端子は、TTLレベルで規定されたLレベル電圧0.4Vになります。

完全に0Vまで下がらないのは、

Q2のコレクタ・エミッタ間飽和電圧Vce(sat)により、

コレクタ・エミッタ間に電圧が残るためです。

この時、TTL の出力には、

プルアップ抵抗とCMOS ICからの電流IOLが流れ込みます。

IOL=(VccーVOL)/R

=(5ー0.4)V/9.98kΩ

=0.46mA

先程のコレクタ・エミッタ間飽和電圧Vce(sat)は

電流が増えると増加するため、出力電圧が上昇します。

TTL ICの出力電圧が1.5Vを超えると、

CMOS ICがLレベルと認識できなくなります。

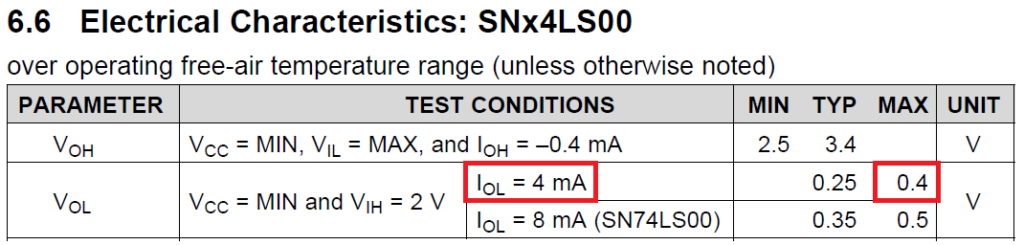

例として、テキサスインスツルメンツ製TTL IC SN74LS00 の場合、

データシートを見ると、VOL=0.4Vを保証する条件がIOL=4mAです。

先ほど計算したIOL=0.46mAなら、VOLが0.4V以下になるので、

Lレベルの認識に問題ないことがわかり、

プルアップ抵抗値が10kΩで適切な事がわかります。

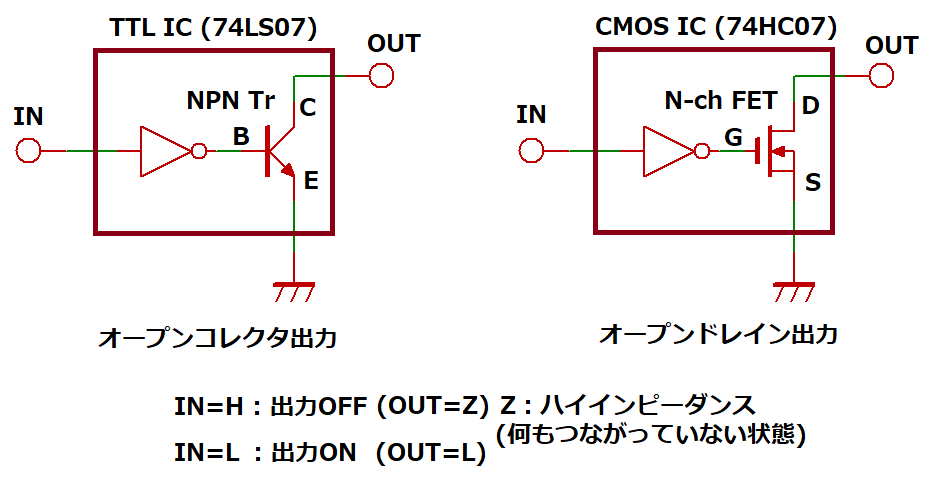

プルアップ抵抗値の決め方(オープンコレクタ出力の場合)

オープンコレクタ出力やオープンドレイン出力を

H又はLレベルの論理信号としてICに入力する場合、

プルアップ抵抗を接続する必要があります。

オープンコレクタは出力がトランジスタのコレクタ(C)、

オープンドレインは出力がFETのドレイン(D)につながっています。

どちらも、出力には電源が供給されていない(オープン)なので、

このままでは電圧を出力できません。

そのため、出力にプルアップ抵抗を介して電源を供給することで、

出力がOFF時はH電圧、ON時はL電圧を出力できます。

オープンコレクタの詳細は下記記事を参照下さい。

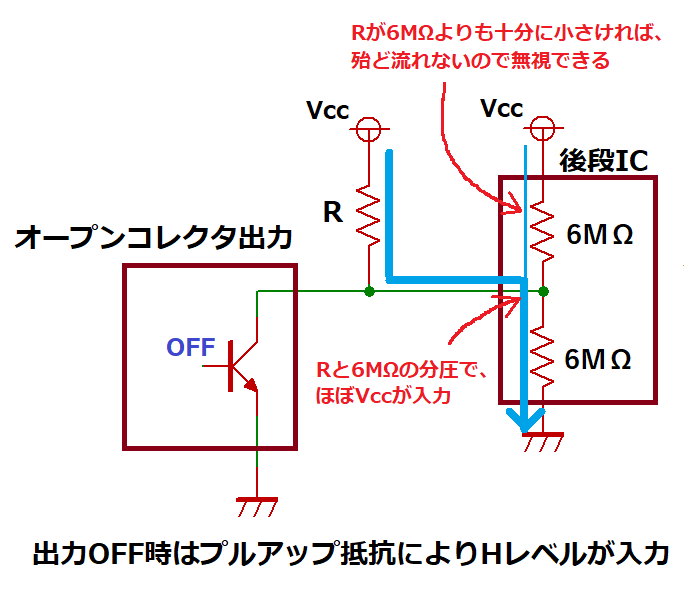

オープンコレクタ出力がOFFの時は、

後段ICの入力にはプルアップ抵抗しか接続されていない状態と同じなので、

そのままHレベル電圧が入力されます。

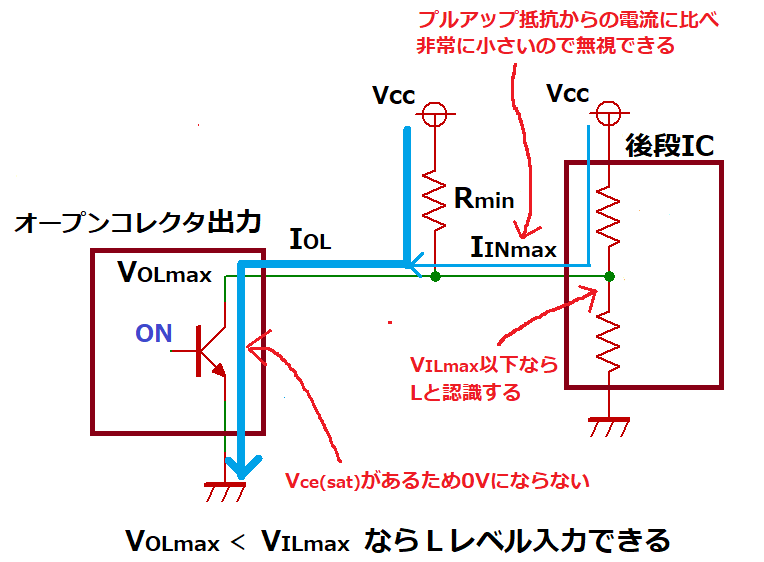

オープンコレクタ出力がONの時は、

前段ICの出力がGNDと接続されるので、

ほぼ0Vとなり、後段ICはLレベルが認識されます。

完全な0Vにならない理由は、

トランジスタにはコレクタ・エミッタ間飽和電圧Vce(sat)があり、

コレクタ・エミッタ間に僅かに電圧が残るためです。

オープンドレインの場合はFETのON抵抗Ronがあるので、

ON抵抗×ドレイン電流により、ドレイン・ソース間に電圧VDSが発生します。

このVce(sat)はコレクタ電流が増えると上昇します。

このため、プルアップ抵抗が小さすぎると、

オープンコレクタ出力に流れ込む電流が増えることで、

Vce(sat)(つまり、オープンコレクタの出力電圧)が上昇し、

後段ICでLレベルと認識できなくなります。

Lレベルを認識できるプルアップ抵抗の下限は、

CMOS出力の場合と同様に以下の式で求めます。

(VccーVOLmax)/IOL<Rmin

SN74LS07の場合、データシートより、

VOLmax=0.4Vで、その時のIOLは16mAなので、

Rmin=(5Vー0.4V)/16mA≒288Ω

となり、プルアップ抵抗は228Ω以上にする必要があります。

上限についても、CMOS出力の時と同じです。

(VccーVIHmin)/IINmax>Rmax

後段ICがTC74HC04の場合は先程計算した1.85MΩとなります

実際に使用される抵抗値はCMOS出力時と同様、4.7kΩや10kΩになります。

プルアップ抵抗値の決め方(接点出力の場合)

入力機器がスイッチやリレー等の接点出力の場合、

接点に流れる電流が小さ過ぎると、

開閉を繰り返すうちに酸化皮膜が生成されて接触不良が発生します。

それを防ぐには、ある程度の電流を流すことで、

アーク放電を発生させて、酸化被膜を破壊させます。

このため、接点出力を持つ機器には、最小電流が規定されており、

この電流値を下回らないようにする必要があります。

下図の様に、スイッチからの入力をプルアップすることで、

スイッチがOFF時はHレベル、ON時はLレベル信号がICに入力されます。

スイッチON時に流れる電流は、プルアップ抵抗からと、

CMOS ICの入力から流れる電流の合計ですが、

ICから流れる電流は1uAと非常に小さいので無視します。

プルアップ抵抗から流れる電流が、

スイッチの最大定格電流を超えないのと同時に、

最小電流を下回らないように抵抗値を決めます。

最小電流については、

スイッチやリレーのデータシートで最小負荷として定義されています。

例として、オムロン製マイクロスイッチZ-01H(定格DC30V 0.1A)の場合、

最小適用負荷がDC5V 1mAです。

従って、このスイッチは1mA~0.1Aの範囲で電流を流す必要があるので、

ここでは、10mA流れるようにプルアップ抵抗を選定します。

R=5V/10mA=500Ω

抵抗値のラインナップ(E24系列)から470Ωを選択します。

スイッチON時に流れる電流は

I=5V/470Ω=10.6mA

になります。

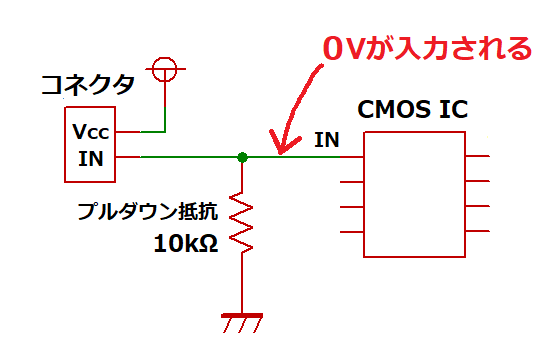

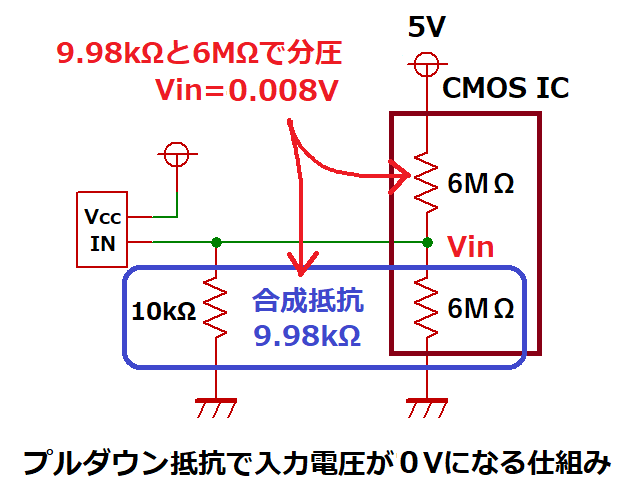

プルダウン抵抗の原理と効果

図のように、GNDにプルダウン抵抗10kΩをつなげると、

ICの入力には0Vが入力されます。

抵抗を経由しているのに入力電圧が0Vになる理由は、

ICの入力抵抗が非常に大きいからです。

プルアップ抵抗の解説で説明した通り、

CMOSロジックIC(TC74HC04)の入力抵抗は6MΩです。

ここで、プルダウン抵抗10kΩが接続されている場合、

10kΩと6MΩの合成抵抗は9.98kΩとなります。

5Vが9.98kΩと6MΩで分圧されるので、

入力電圧Vinは0.008Vとなり、ほぼ0Vが入力されます。

プルダウン抵抗値の決め方(CMOS ICの場合)

入力機器がCMOS出力の場合、

プルダウン抵抗値は以下になります。

・プルダウン抵抗の上限値:Rmax

VILmax/ IINmax > Rmax

VILmax:後段ICの最大Lレベル入力電圧

IINmax:後段ICの最大入力電流

・プルダウン抵抗の下限値:Rmin

VOHmin/ IOH < Rmin

VOHmin:前段ICの最小Hレベル出力電圧

IOH:前段ICのHレベル出力電流(VOHmin出力時)

上記の式になる理由を以下で説明します。

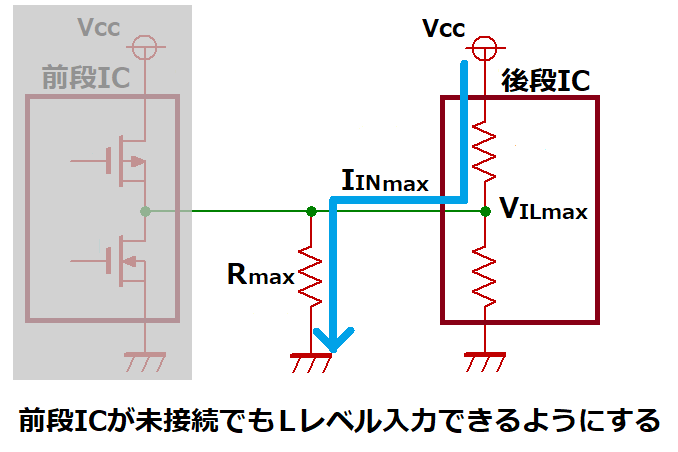

<上限値の決め方>

まず、前段ICが未接続で電圧が入力されなくても、

プルダウン抵抗だけで、Lレベルと認識できるようにする必要があります。

後段ICにプルダウン抵抗を接続すると、

ICから入力電流が流れるので、プルダウン抵抗の両端に電圧が発生します。

このプルダウン抵抗に発生した電圧によって、

後段ICの入力電圧が最大Lレベル入力電圧VILmaxより高くなると、

Lと認識できなくなります。

このため、プルダウン抵抗に発生する電圧が、

VILmaxより低くなるようにします。

VILmax >(Rmax × IINmax)

変形すると、先ほどの式になります。

VILmax / IINmax > Rmax

TC74HC04の場合、データシートより、

VILmax=1.35V、IINmax=1uAなので、

1.35V/1uA=1.35MΩ>Rmax

となり、プルアップ抵抗は1.35MΩ以下にする必要があります。

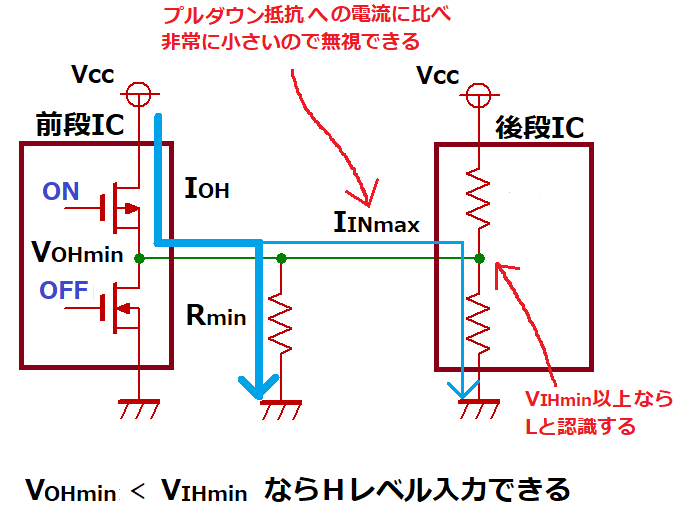

<下限値の決め方>

後段ICにH信号を入力するには、

前段ICの出力電圧をHレベルまで上げる必要があります。

しかし、プルアップ抵抗が小さすぎると、

前段ICからの出力電流が大きすぎて、

出力電圧が低下し、後段ICでHと認識できなくなります。

前段ICのデータシートを見ると、

最小Hレベル出力電圧VOHminと、

その時に流れる電流IOHが規定されています。

つまり、前段ICからの出力電流がIOH以内なら、

出力電圧はVOHmin以上であることを意味します。

前段ICのHレベル出力電圧VOHmin>後段ICのHレベル入力電圧VIHmin

ならば、後段ICでHと認識できます。

このため、プルアップ抵抗に流れる電流を

IOHよりも小さくなるようにします。

VOHmin/Rmin<IOH

厳密には、後段ICへも電流が入力されますが、

最大でも1uAと、プルダウン抵抗に流れる電流(mAレベル)

に比べて非常に小さいため、無視できます。

変形すると、先ほどの式になります。

VOHmin/ IOH < Rmin

TC74HC04の場合、データシートより、

VOHmin=4.13Vで、その時のIOHは4mAなので、

Rmin=4.13V/4mA≒1.03kΩ

となり、プルダウン抵抗は1.03kΩ以上にする必要があります。

以上の結果から、

1.03kΩ<プルダウン抵抗<1.35MΩ

となります。

抵抗値の範囲がかなり広いですが、プルアップ抵抗が大きいと、

H→L時の立下り時間が長くなるので注意が必要です。

理由はプルアップ抵抗の時と同様、CMOS ICの入力はコンデンサに置き換えることができ、

プルダウン抵抗が大きいと、コンデンサの放電に時間がかかるため、立下り時間が長くなります。

実際に使用される抵抗値は、プルアップ抵抗と同様、4.7kΩや10kΩが使われています。

プルダウン抵抗値の決め方(トランジスタの場合)

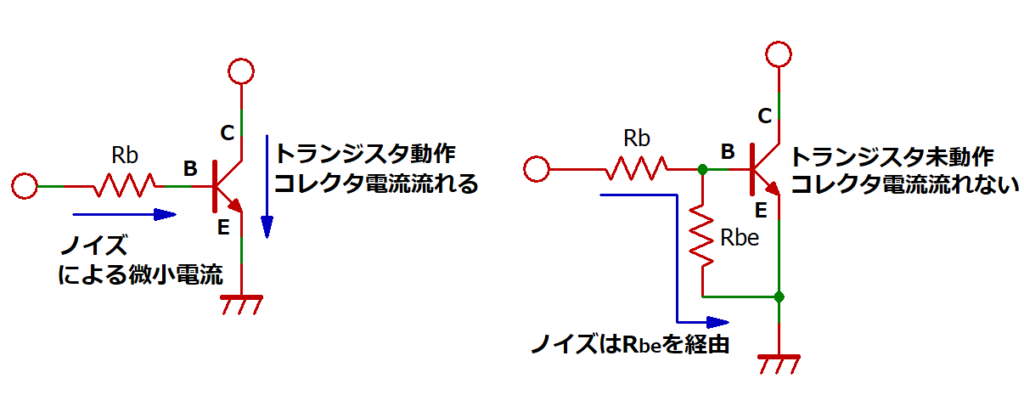

NPNトランジスタのベース信号をプルダウンすることで、

以下の2つの効果があります。

・ノイズによる誤動作を防止

入力電圧が0Vでも、ノイズが入ると微小とはいえ、ベースに電流が流れ込みます。

それによって、コレクタ電流Icが流れ、トランジスタがONしてしまいます。

ベース~エミッタ間にプルダウン抵抗Rbeをつけると、

ノイズで発生した電流がRbeを介してエミッタ(GND)に流れることで、

ベース電流が0となり、コレクタ電流Icは流れず、トランジスタはOFFを維持できます。

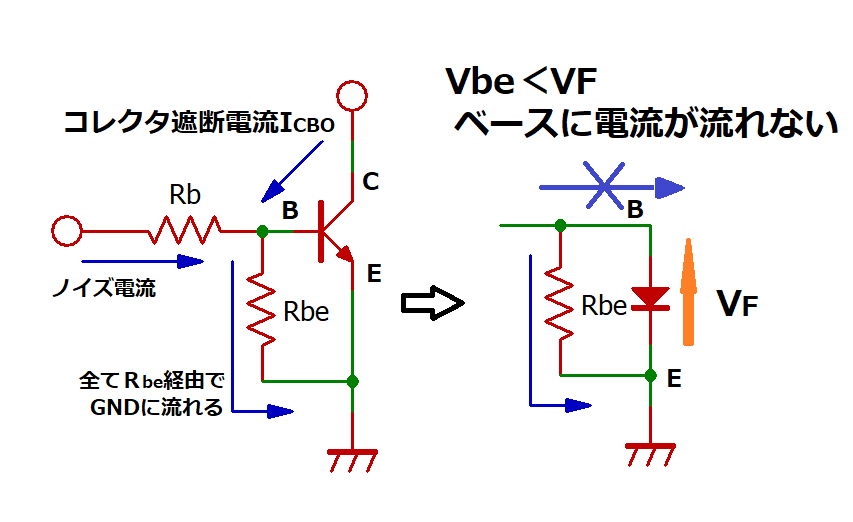

・コレクタ遮断電流による誤動作を防止

NPNトランジスタの場合、コレクタ・ベース間は逆方向ダイオードになるので、

コレクタからベースへ電流は流れない筈ですが、

実際には漏れ電流(逆方向電流)が少しだけ流れます。

これをコレクタ遮断電流ICBOと呼び、

例えば、2SC1815のデータシートを見ると、ICBO=0.1uAです。

この0.1uAがベースに流れ込んだ場合、電流増幅率hfeが100なら

コレクタ電流Icは100倍の10uA流れることになります。

Rbeをつけることで、コレクタ遮断電流をエミッタ側に流し、

ベースに電流が流れないようにすることで、トランジスタがONしないようにします。

<プルダウン抵抗Rbeの決め方>

Rbeは一般的に1k~10kΩが使われています。

理由ですが、ノイズ電流が0.1uA、コレクタ遮断電流Iceoが0.1uA流れたとした場合、

Rbeが1k~10kΩならば、

Rbe間電圧=Rbe × 0.2uA =0.2mV~2mV

になります。

Rbe間の電圧=トランジスタのBE間電圧Vbeです。

このBE間は順方向ダイオードに置き換えることができ、

BE間電圧がダイオードの順方向電圧VFより低いと

ダイオードは電流を流すことができません。

このVFですが、トランジスタのデータシートでは、

ベースエミッタ間飽和電圧Vbe(sat)で表現されており、

一般的に0.6V程度です。

BE間電圧がVbe(sat)より十分低い電圧なので、ベースに電流が流れず、

Rbeを経由してGND(エミッタ)に流すことで、誤動作を防止できます。

一方、トランジスタをONさせる場合、必要な電流Iは、

ベース電流IBと、Rbeに流れる電流IRBEの合計になります。

I=IB+IRBE

IRBEは以下の式で求まります

IRBE=Vbe(sat)/Rbe

=0.6V/1k~10kΩ

=0.06~0.6mA

このため、Rbeを小さくすると、その分、トランジスタをONする時に

必要な電流Iが増えてしまうので、数kΩ程度が適切であることがわかります。

詳細は下記で解説しています。

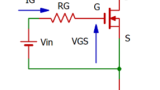

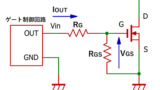

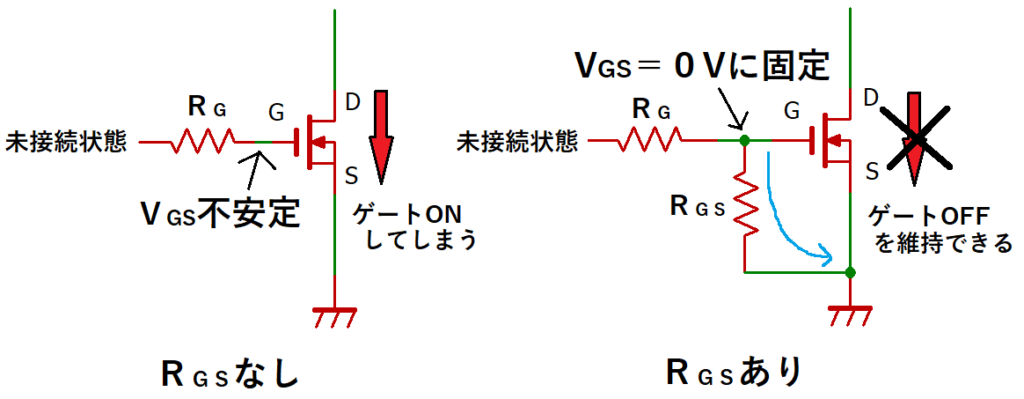

プルダウン抵抗値の決め方(FETの場合)

N-ch MOS FETのゲート信号をプルダウンすることで、

以下の2つの効果があります。

・ゲート信号が未入力時、FETがオンするのを防止

プルダウン抵抗RGSをつけることで、ゲート信号が入力されない場合でも、

ゲート電圧が0Vに固定されることで、オンすることを防ぎます。

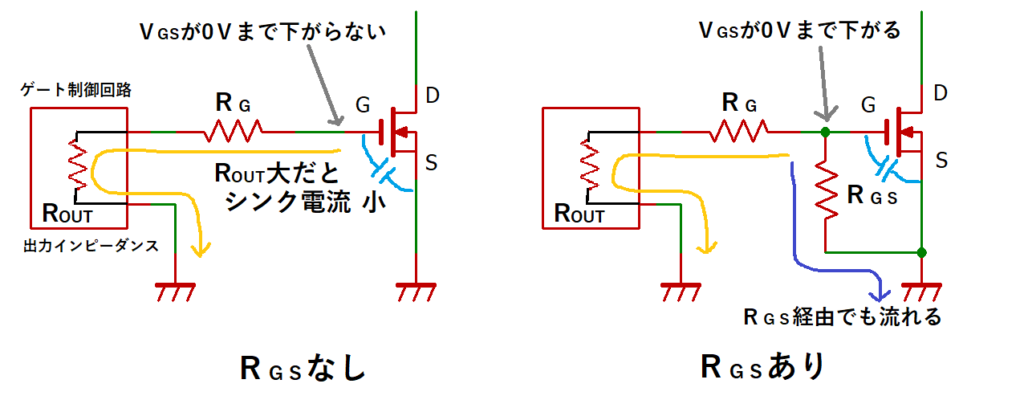

・ゲート制御回路がVGS=0Vにするのをサポートする

FETのG-S間はコンデンサに置き換えることができます。

FETをOFFする際にVGSを0Vにしますが、

そのためには、コンデンサに充電された電荷を放電させる必要があります。

ゲート制御回路の出力インピーダンスRoutが大きいと、シンク電流が小さくなり、

コンデンサが十分に放電されず、VGSが0Vまで下がらない場合があります。

RGSをつけることで、コンデンサの電荷をRGS経由でも流すので、

十分に放電することができ、Routが大きくてもVGSを0Vまで下げることができます。

プルダウン抵抗RGSの決め方については、

以下の3つの条件を満たすようにします。

・RGS > 10 x RG

ゲート抵抗RGの10倍以上の値にする。

※RGの決め方は「ゲート抵抗の決め方」を参照。

・RGS > Vout/ Iout

ゲート制御回路から電流が流れすぎないようにする。

Vout :ゲート制御回路の出力電圧

Iout :ゲート制御回路の出力電流(ソース電流)

・RGS < Vth / Iin

ノイズ電流がゲートに入ってもONしないようにする。

Vth:FETのしきい値電圧*

Iin:ノイズ電流(数uA程度)

*しきい値電圧はFETのデータシートに記載

上記の3つの条件になる理由については下記で解説しています。

これらの条件を満たすRGSの抵抗値ですが、

一般的には4.7kΩ~22kΩの範囲(10kΩが最も多い)であれば基本的には問題ないです。

以下の記事で、半田付けのコツや部品の外し方を解説しています。