この記事でわかること

・プッシュプル回路の動作と用途が理解できる。

・プッシュプル回路の設計方法がわかる。

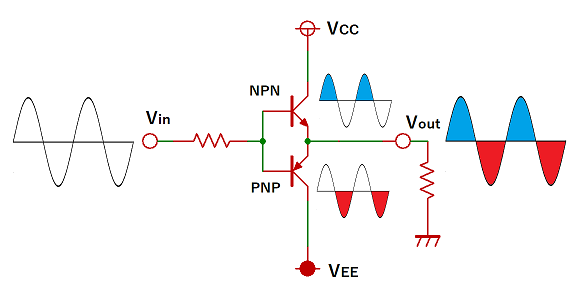

プッシュプル回路の原理

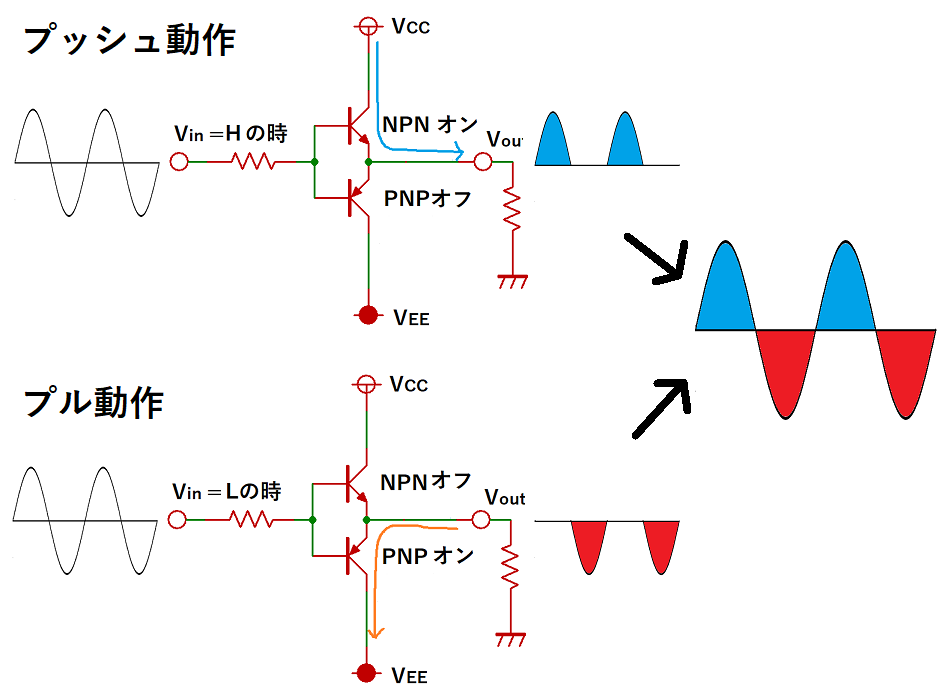

NPNとPNPトランジスタを2段に接続した回路構成です。

電流が流れだす動作(プッシュ)と流れ込む動作(プル)を交互にするので、

プッシュプルと呼ばれ、別名、トーテムポール回路とも呼ばれます。

トーテムポールは、アメリカ先住民族が作った柱状の木造彫刻で、トランジスタを2段にした構成が似ていることから来ています。

昔は小学校の校庭によくあったので、私はイメージがつくのですが、今はこの例えで分かるのでしょうかね?

入力電圧Vin=Hの時、NPNがオン、PNPがオフするので、出力電圧VoutがHになります。

Voutから負荷に電流が流れます。

(負荷への供給源(source)になるのでソース電流と呼びます)

入力電圧Vin=Lの時、NPNがオフ、PNPがオンするので、出力電圧VoutがLになります。

Voutに負荷から電流が流れ込みます。

(キッチンのシンク(sink)のように流れ込むのでシンク電流と呼びます)

プッシュプル回路の利点と用途

利点ですが、トランジスタ1個に比べ、電流が多く流せて高効率です。

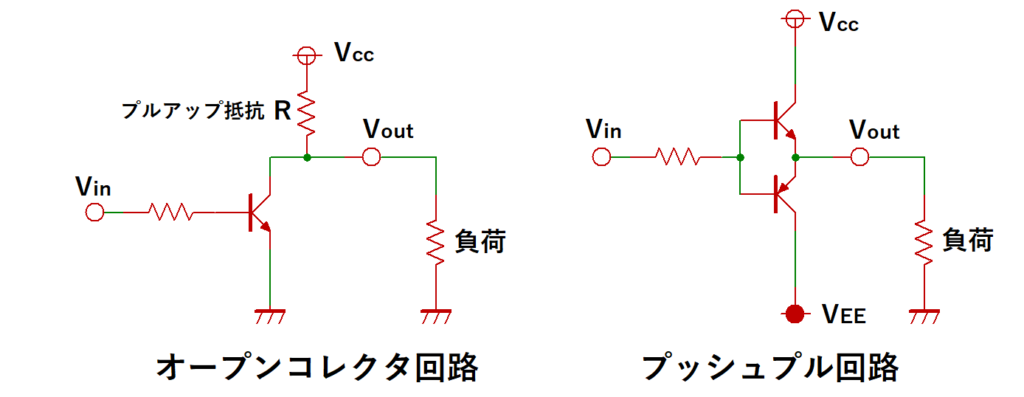

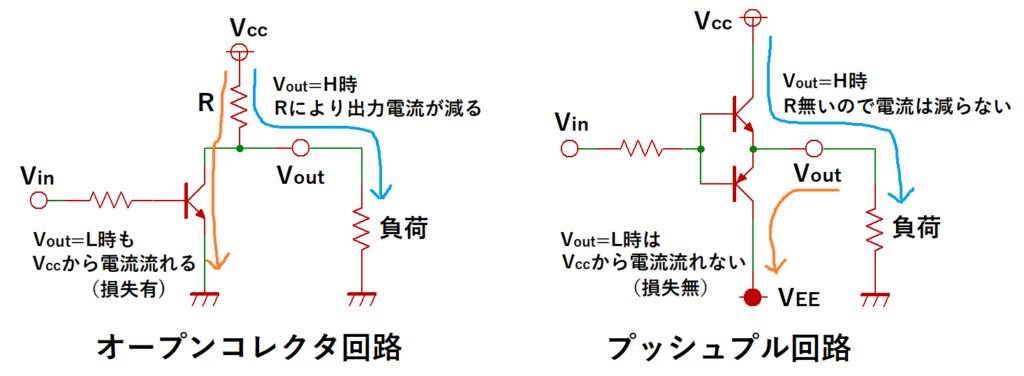

1個の場合(オープンコレクタ出力)と比較してみます。

※オープンコレクタ出力については、「オープンコレクタとは?接続方法とNPNとPNPの違いについて」を参照

オープンコレクタの場合、Vout=H時は電源Vccからプルアップ抵抗Rを経由するので、

Rが大きいと、負荷に供給できる電流が減ってしまいます。

また、Vout=Lでもトランジスタを経由して電流が流れるので、電力を消費します。

このため、Rが小さいと損失が大きくなり、効率を悪化させてしまいます。

プッシュプルはプルアップ抵抗が不要なので、負荷に供給する電流が減りません。

そして、出力L時は電源Vccから電流は流れないので損失が発生せず、高効率にできます。

用途としては、信号増幅やスイッチング制御に用いられます。

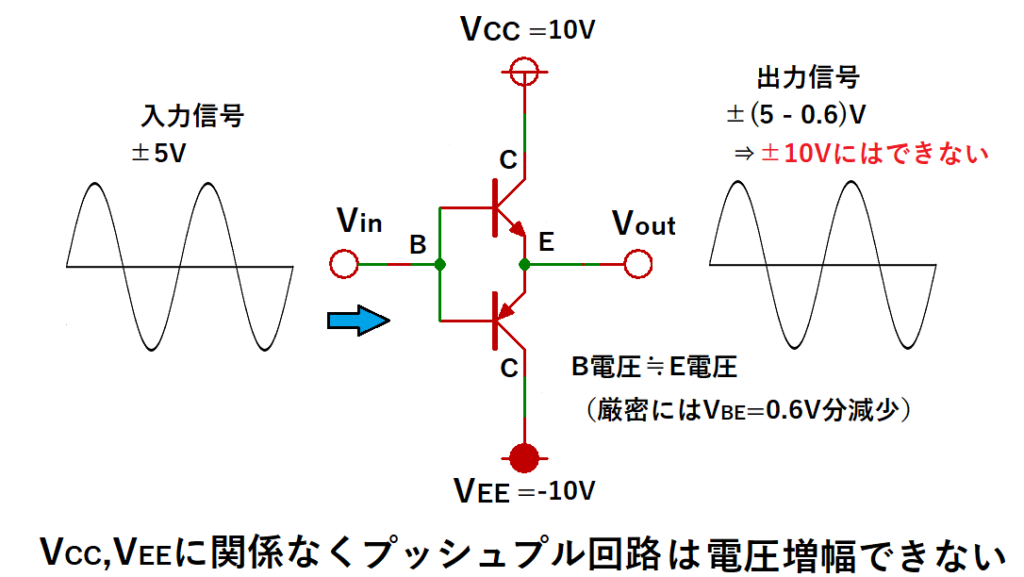

増幅といっても、電流は増やせますが、電圧は入力電圧より大きくできません。

(むしろ、ベース・エミッタ間電圧分、0.6V程度低下します)

これはトランジスタが、

「エミッタ電圧はベース電圧よりも0.6V低下する」

という特徴を持っている為です。

※この理由については、「シリーズレギュレータ、リニアレギュレータの設計方法」を参照。

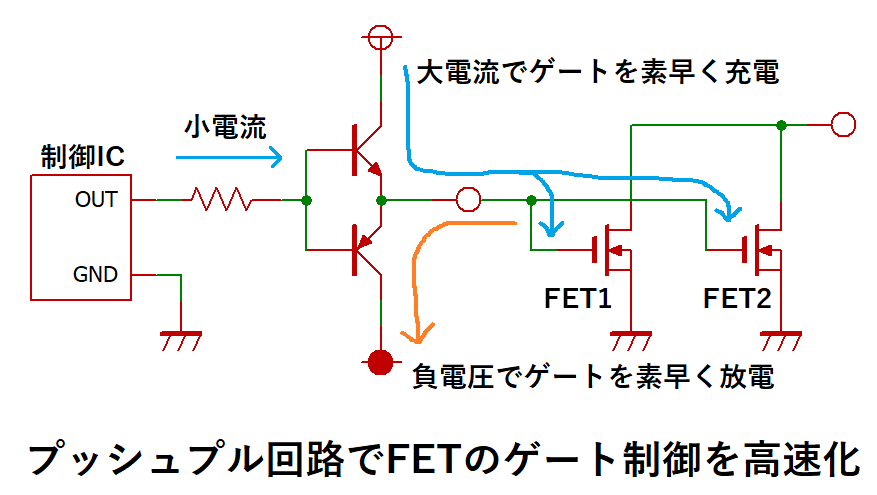

スイッチング制御については、複数のFETを同時に制御する等、大きなゲート電流を流したいが、制御ICの出力電流だと不足する場合に使用されます。

※ゲート入力はコンデンサと考えてよいので、このコンデンサの充放電を素早くおこなう必要があります。

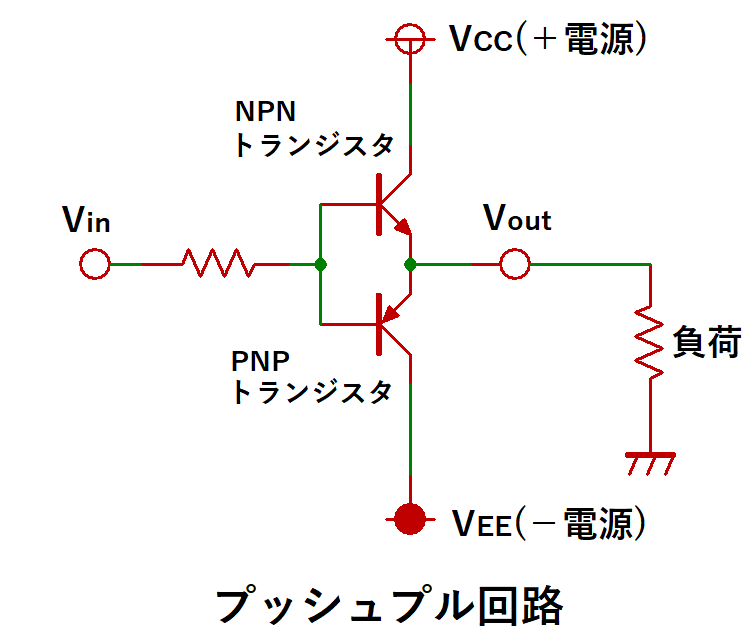

コンプリメンタリ(相補)とは?

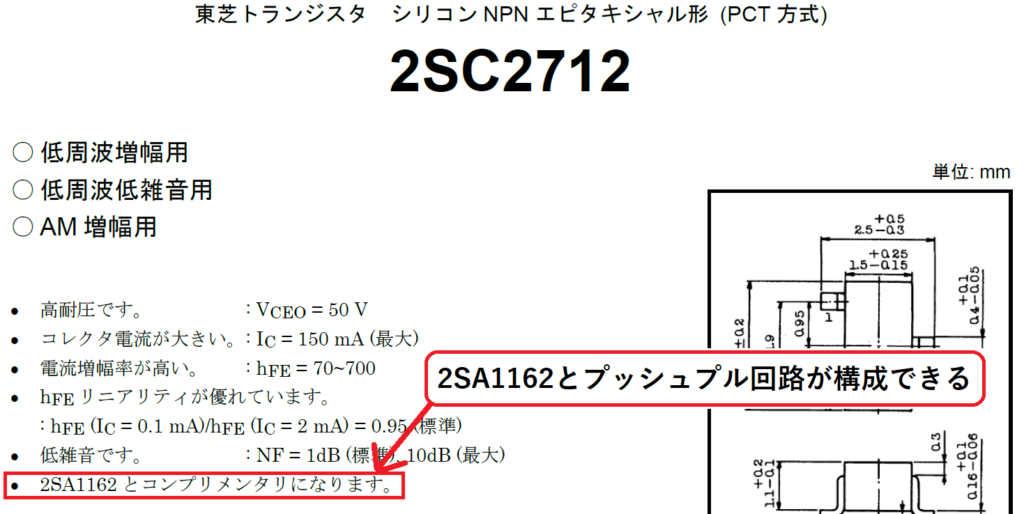

プッシュプル回路を構成するには、コンプリメンタリ(相補)のトランジスタを使います。

コンプリメンタリ(相補)とは、PNPとNPNで同じ特性を持つことを意味します。

特性が揃っていないと、ON/OFFのタイミングが合わない、増幅率が違う等の理由により、

出力波形が上下対象でなくなり歪んでしまいます。

データシートに「○○とコンプリメンタリになります」と記載したものを選ぶようにします。

プッシュプル回路による増幅回路の設計

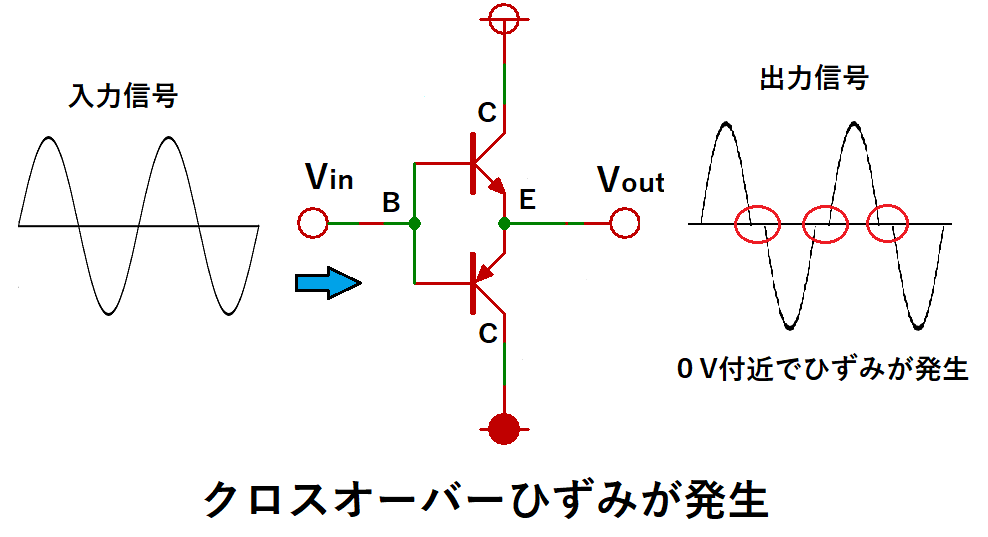

入力が交流信号の場合、マイナス電圧を出力する必要があるので、負電源が必要になります。

この時、プッシュプル回路の出力が0V付近では下図のように歪んだ波形になります。

これをクロスオーバーひずみと呼びます。

ひずみの原因は、入力が0V付近でトランジスタが上下とも動作しなくなるためです。

動作しなくなる訳は約0.6Vのベース・エミッタ間電圧VBEにあります。

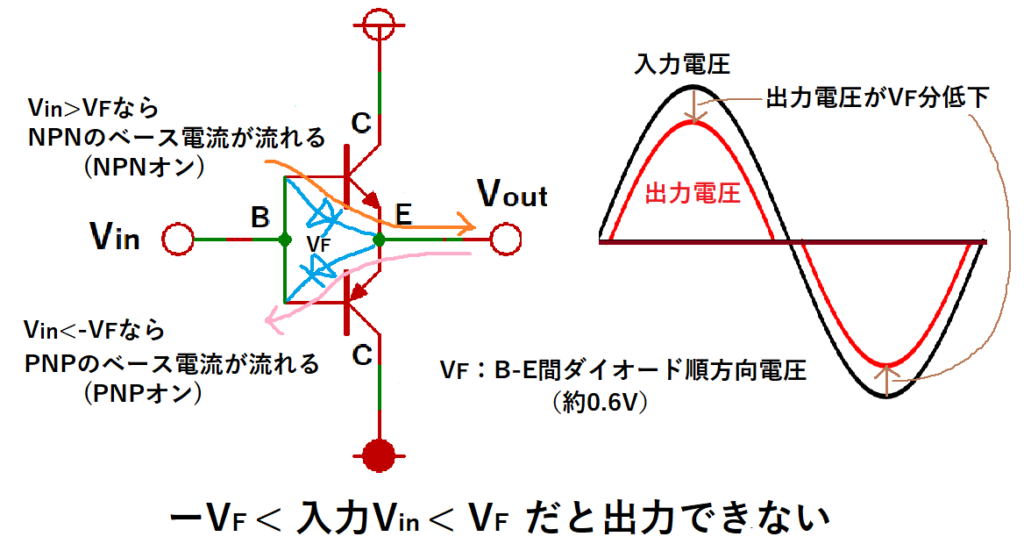

その仕組みはトランジスタのベース・エミッタ間をダイオードに置き換えると分かりやすいです。

ダイオードには順方向電圧VFがあり、これより印加電圧を大きくないと電流が流れません。

つまり、ベース電流が流れない(トランジスタがオンしない)という訳です。

一般的なトランジスタは、このVFが0.6V程度であることから、VBEも0.6Vになります

入力VinがNPNトランジスタのベース・エミッタ間電圧VBEより低いと、

ベースに電流が流れないためONできません。

PNPも同様で、VinがVBEより高いと、ベース電流が流れないのでオンできません。

従って、-0.6V<Vin<+0.6Vの範囲では上下トランジスタともオンできず、

出力電圧0となるので、波形が歪みます。

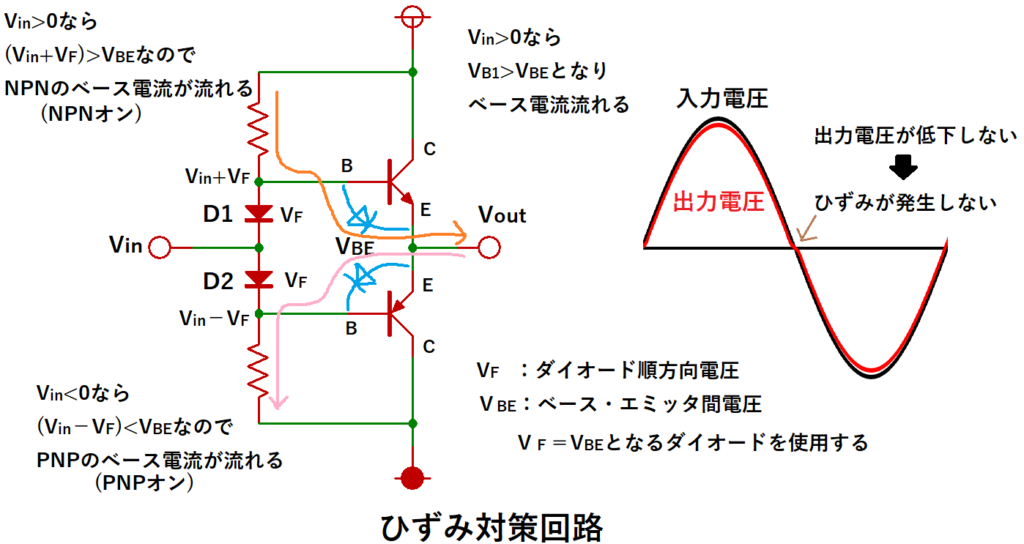

対策はダイオードを挿入することでVin=0V付近でもトランジスタがオンできるようになります。

ダイオードの順方向電圧VFはトランジスタのVBE電圧と同じ0.6Vのものを選ぶようにします。

Vin=0V時、NPNのベース電圧はダイオードD1の順方向電圧VF分高い電圧になります。

VF=VBEならば、Vinが0Vより少しでも上昇すれば、ベース電圧がVBEより高くなるので、

NPNがオンします。

同様に、PNPのベース電圧はダイオードD2の順方向電圧VF分低い電圧になるので、

Vinが0Vより少しでも下降すれば、ベース電圧がVBEより低くなるので、PNPがオンします。

これによって-0.6V<Vin<+0.6Vの範囲でもトランジスタが動作するようになり、

ゆがみを無くすことができます。

しかし、実際はVFとVBEは温度や電流によって変化するので、

完全にVF=VBEにすることは困難です。

このため、VF<VBEなら、上下ともオフするため、波形の歪みが発生します。

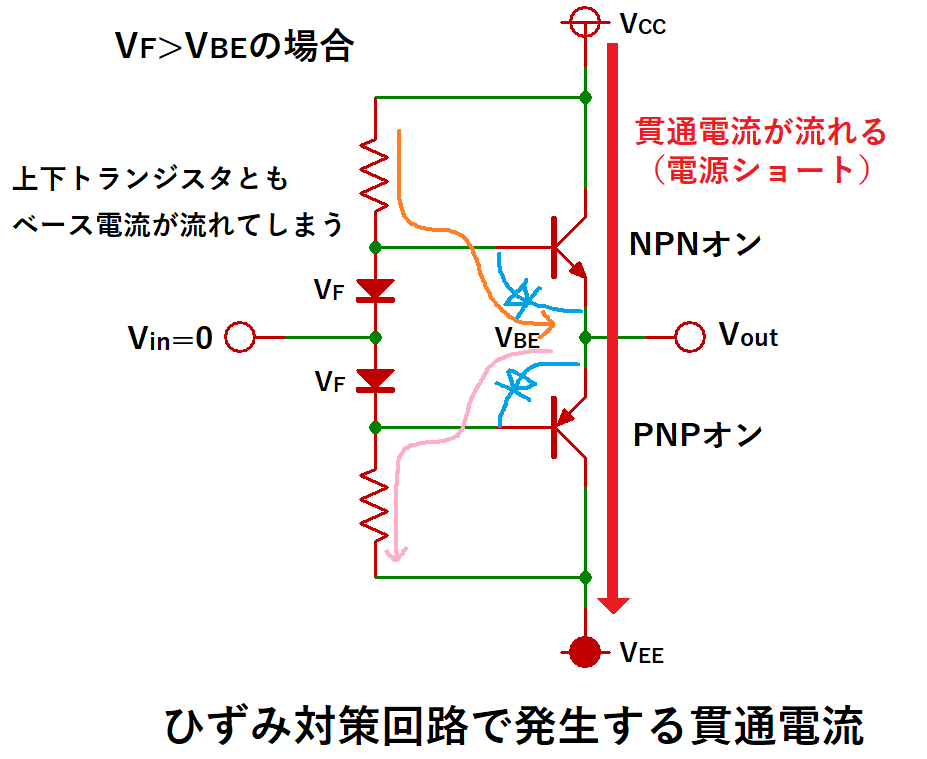

逆に、VF>VBEでは、上下ともオンして、電源ショート状態になります。

この時、流れる電流を貫通電流といいます。

この貫通電流が過大だとトランジスタが壊れる場合があるので、

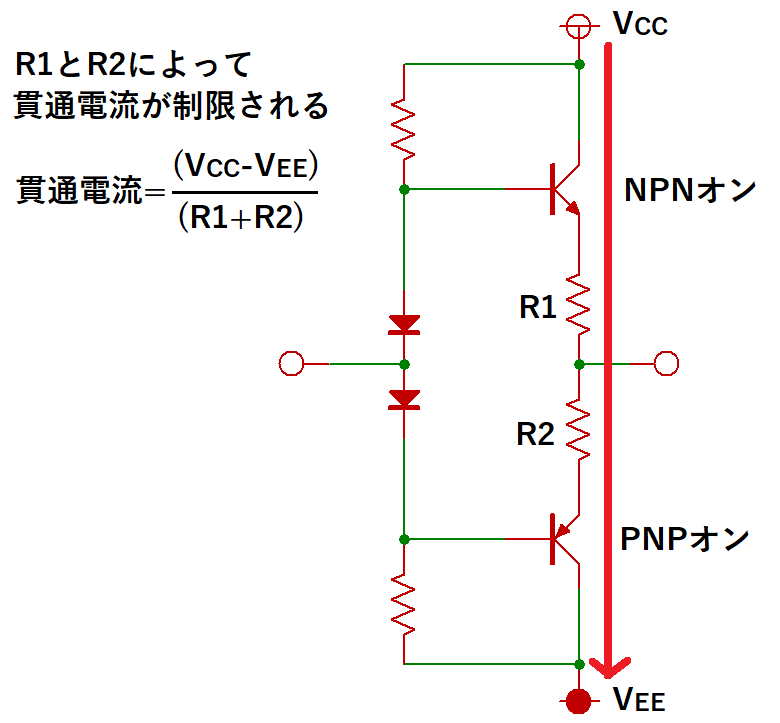

電流を制限する抵抗を挿入します。

抵抗値は貫通電流が流れても、トランジスタの最大コレクタ電流を超えない値にします。

ここで、最大コレクタ電流が小さいトランジスタだと、制限抵抗を大きくする必要があり、

その分、通常動作時の出力電流が減ってしまいます。

このため、最大コレクタ電流が十分に大きいトランジスタを選ぶようにします。

そうすることで、制限された最大電流でも負荷にとって十分な電流供給ができるようにします。

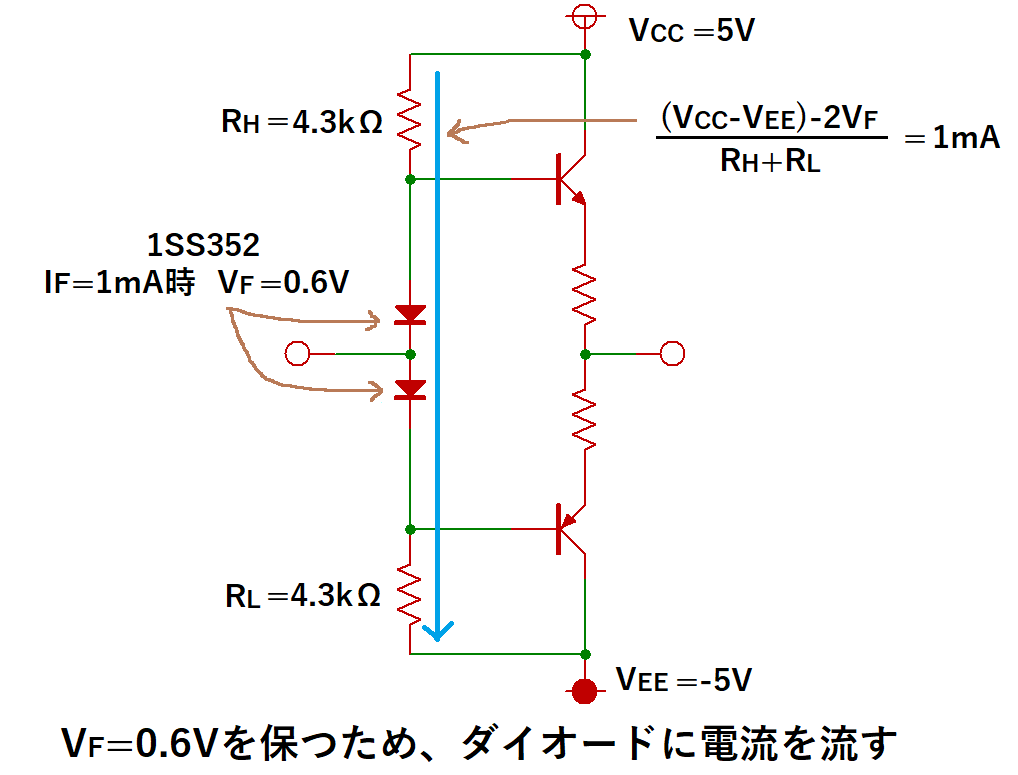

また、この対策ではVFを一定に保つため一定の電流をダイオードに流す必要があります。

例えばダイオード1SS352の場合、データシートよりVF=0.6VにするにはIF=1mA必要なので、抵抗RH、RLは4.3kΩにします。

この電流は、常に流れるのでIFが大きいダイオードを使うと損失が大きくなります。

プッシュプル回路によるスイッチング制御回路の設計

スイッチング制御に適用する場合、基本的には増幅回路と同じ回路構成になりますが、

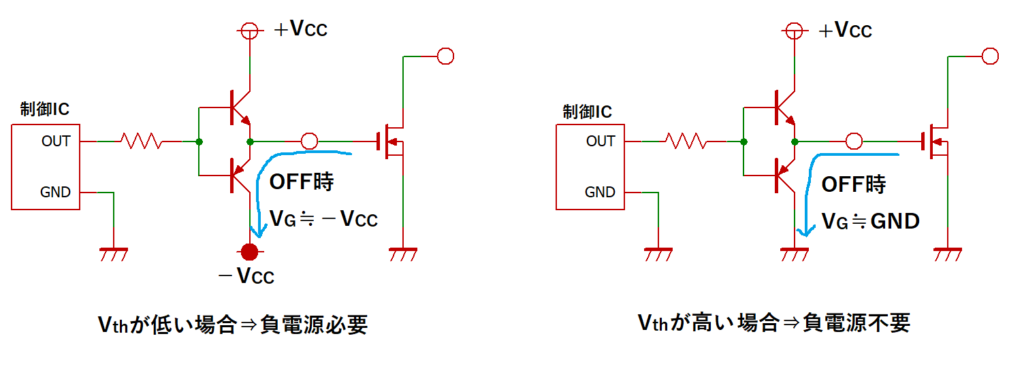

制御するFETのしきい値電圧Vthがある程度高い(3V程度)場合、負電源は不要です。

理由ですが、負電源(-Vcc)を使用した場合、プッシュプル出力L時の出力電圧は-Vccになります。

(厳密にはコレクタ・エミッタ間飽和電圧Vce(sat)分=0.1V程度減って、-Vcc+0.6V)

負電源を使用しない場合は、出力電圧は0Vになります。

(これも厳密にはVce(sat)=0.1Ⅴ程度になります)

FETをオフするには、ゲート電圧VGをしきい値Vthより低くする必要があります。

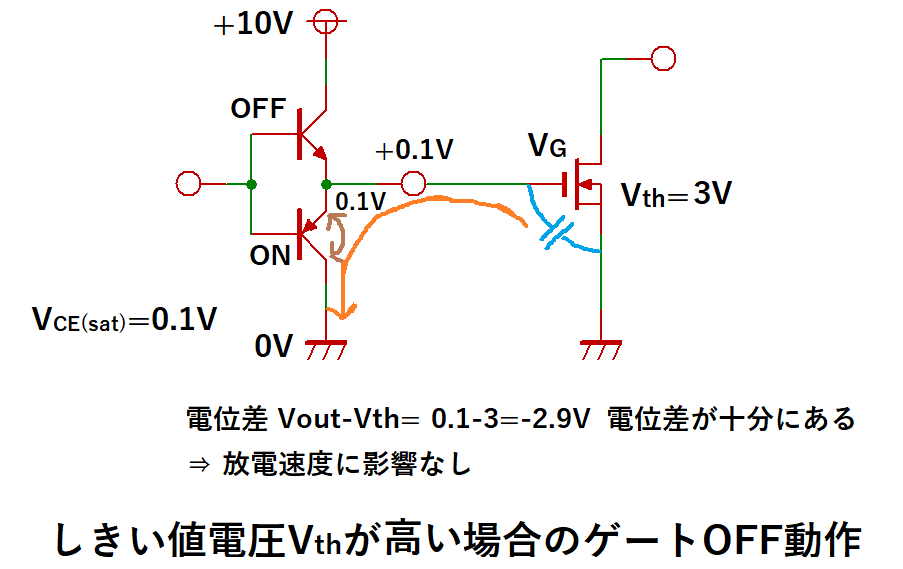

ゲート入力はコンデンサに置換えでき、コンデンサの電荷を放電させることでVGを下げます。

Vthが3V程度と高ければ、プッシュプルの出力が0.1V程度まで下がれば十分な電位差ができるので、ゲート内の電荷を引き抜くことができます。

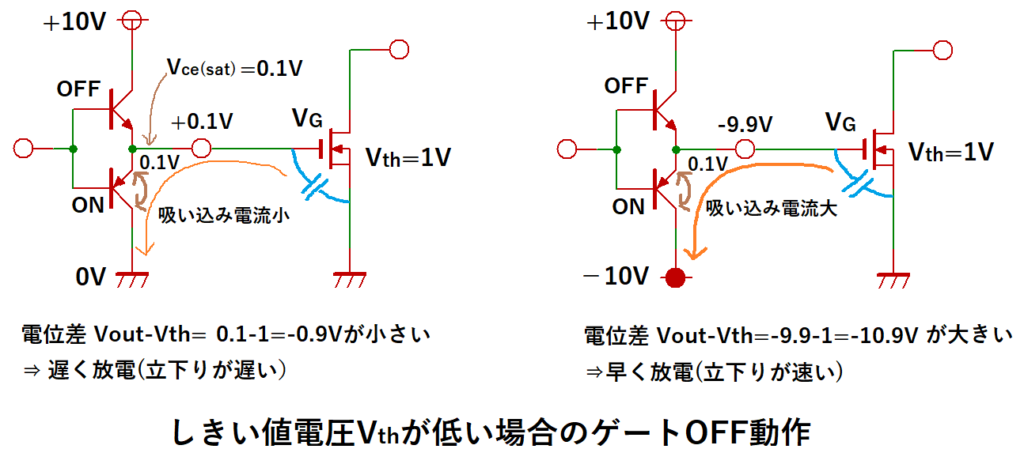

Vthが1Ⅴ以下と低い場合は、プッシュプルの出力を0.1Vまで下げても電位差が小さいので、

ゲート内の電荷を素早く引き抜くことができず、ゲートOFFが遅くなってしまいます。

このような場合は、負電源を利用して出力をマイナス電圧まで下げることで電位差を確保する必要があります。

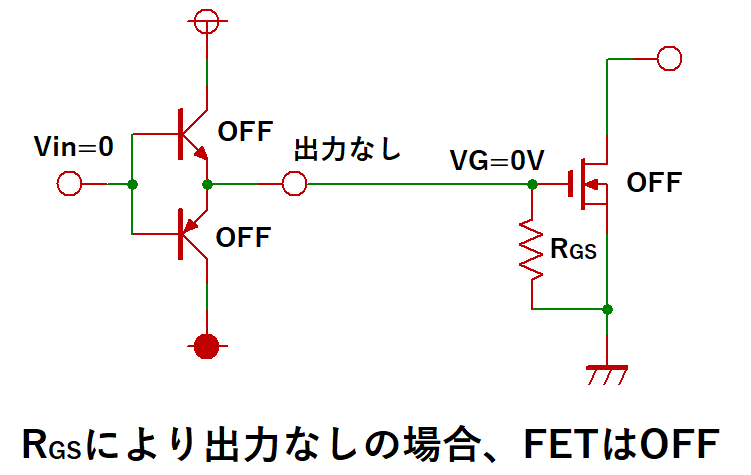

スイッチングの場合は、プッシュプルの出力はしきい値電圧より十分高いか、低ければよく、

0V付近の波形の歪みを気にする必要はないので、ダイオードによる歪み防止対策は使いません。

もし、上下ともトランジスタがOFFになり出力が出なくても、FETが不安定動作にならないように10kΩ程度のゲート・ソース間抵抗RGSをつけておけば、未出力時はVG=0Vになるので問題ありません。

<トランジスタの詳細については下記の記事で解説しています>

<回路工作で役立つ工具類を下記の記事で紹介しています>