この記事で分かること

MOSFETのゲート抵抗値の計算方法がわかる。

MOSFETにゲート抵抗がついている理由と、ゲート抵抗値の求め方について説明します。

FETは大別して、接合型(JFET)とMOS型(MOSFET)があります。

本記事では、MOSFETを単に「FET」と呼ぶことにします。

結論 FETのベース抵抗値 計算式

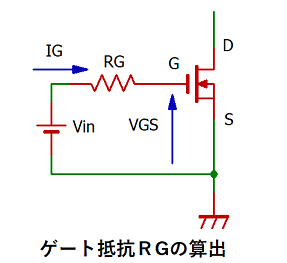

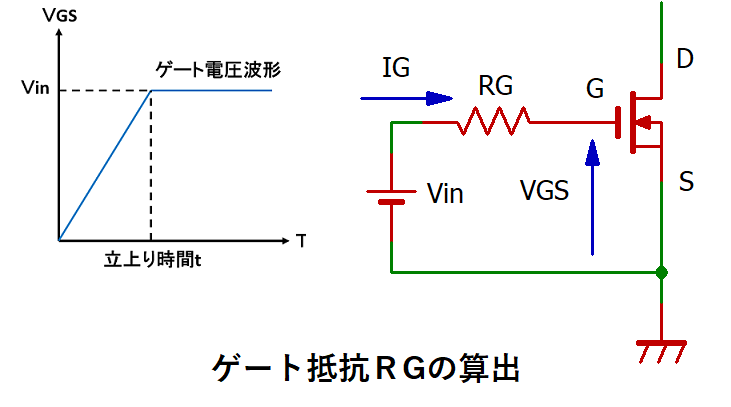

ゲート抵抗RGは以下の計算で決まります。

RG=Vin / IG

ここで、

Vin:入力電圧

IG:ゲート電流

IG = Qg / t

Qg:ゲート入力電荷量[nC]*

t:ゲート電圧の立上り時間[ns]

*はFETのデータシートに記載

*のQgはFETのデータシートに記載されているので、

入力電圧Vinと、ゲート電圧の立上り時間tで求まります。

この式になる理由について説明します。

FETのゲート抵抗値の決め方

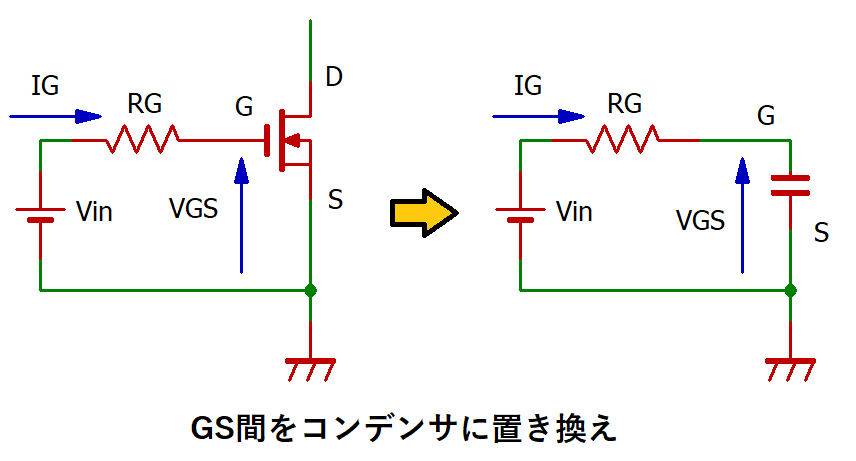

FETのゲート(G)-ソース(S)間はコンデンサに置き換えて考えることができます。

FETをオンさせるにはVGSに電圧を加える必要があるので、

このコンデンサを充電することになります。

このコンデンサを充電してVGSが決められた電圧(10Vが多い)になるのに必要な電荷量が、

ゲート入力電荷量Qgになります。

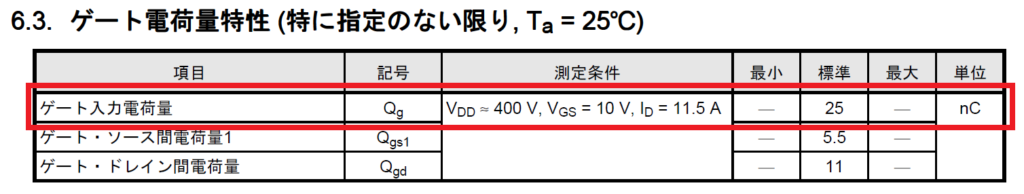

QgはFETのデータシートに記載されています。

この例の場合、入力電圧Vin=10Vにした場合は、このQgの値25nCを使用します。

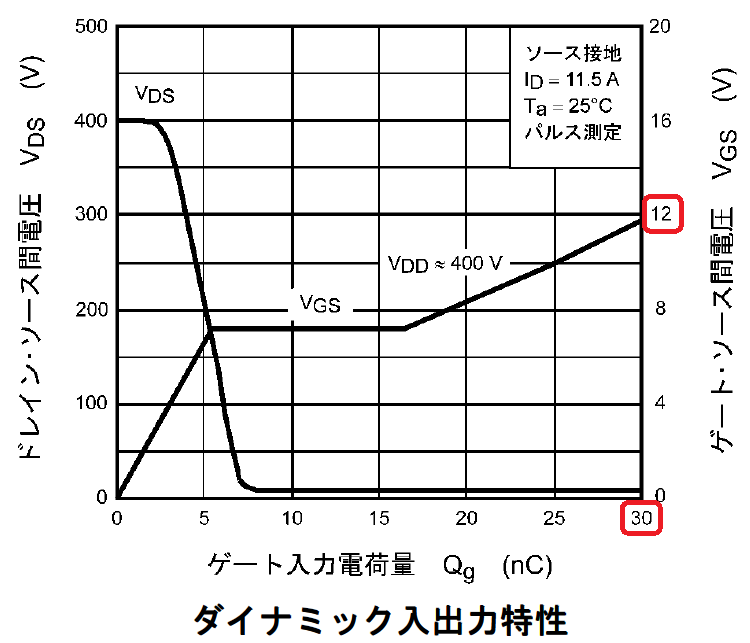

10Vでない場合は、データシートのQg-VGSグラフ(ダイナミック入出力特性)を参照し、

使用するVGSに相当するQgを使用します。

Vin=12Vの場合、このグラフよりQg=30nCとなります。

Qgはゲート電流IGをt時間流して充電されると考えると

Qg=IG x t

となるので、ゲート電流IGは

IG = Qg / t ・・・・(1)

となります。

※厳密にはミラー効果により、ゲートから見た容量が変化して、IG 一定ではないのですが、

大きな影響はないので、簡略化しています。

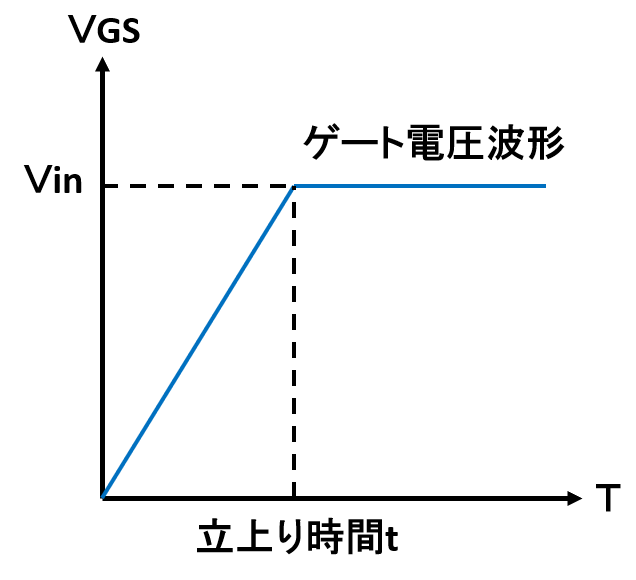

tはゲート電圧がVinまで達する時間、つまり立上り時間になります。

立上り時間tを決めれば、ゲート電流IG が決まります。

よって、ゲート抵抗RGは、

RG=Vin / IG ・・・・(2)

となります。

以上から、ゲート電圧の立上り時間tを決めれば、ゲート抵抗RGが求まります。

このtをどの程度にするかは、以下の事を考慮する必要があります。

<立上り時間tが短い場合>

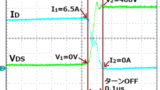

VGSの立上りを早くなり高速化できますが、以下の問題があります。

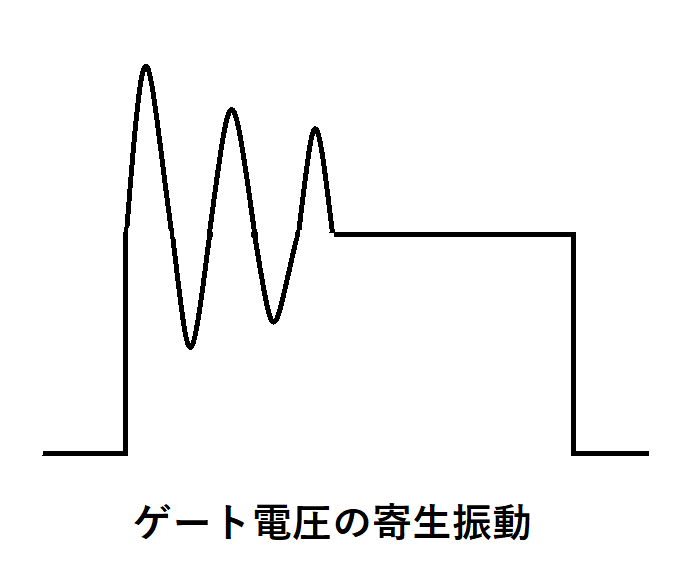

・ゲート電圧に寄生振動が発生してFETが壊れる。

ゲート抵抗が小さいと、コンデンサ成分とリードによるインダクタンス成分が共振を起こして

大きな振動波形が発生し、VGSの最大定格を超えたり、誤動作を起こしてFETが

破壊する恐れがあります。

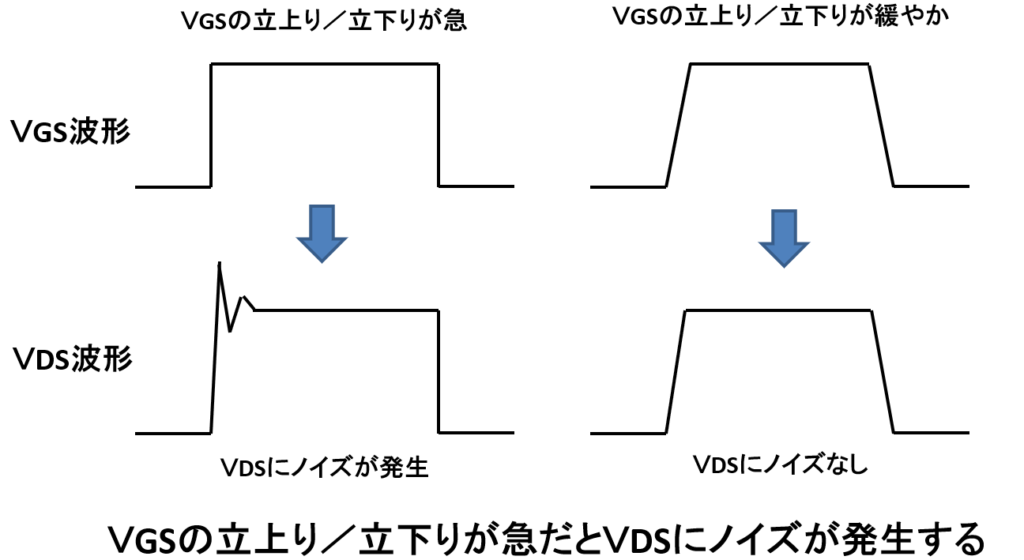

・ドレイン電圧VDSの立上り/立下りが早すぎて、ノイズが大きくなる。

VGSの立上り/立下りが急速なので、その分VDSも急速に変化します。

高電圧スイッチングの場合、大きなノイズが発生し、他の回路に影響を与えたり、

EMC試験で放射ノイズが大きくなり、規制をクリアできなくなる場合があります。

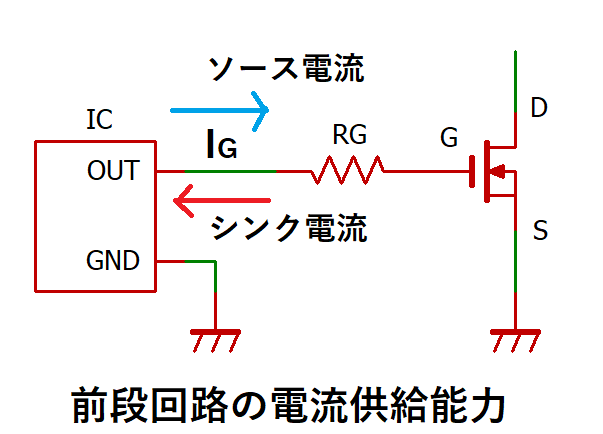

・ゲート電流IG が大きすぎて、FET前段の制御回路が壊れる。

IG が制御回路の電流供給能力(ソース電流/シンク電流)を超えると

回路が故障する場合があります。

<立上り時間tが長い場合>

VGSの立上りを遅くでき、上記の問題がなくなりますが、以下の問題が出てきます。

・スイッチングが遅くなることで損失が増大し、高熱でFETが故障する。

FETはON⇔OFFの切り替え時は損失が大きく、

この時間が長すぎると発熱でFETが壊れる場合があります。

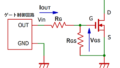

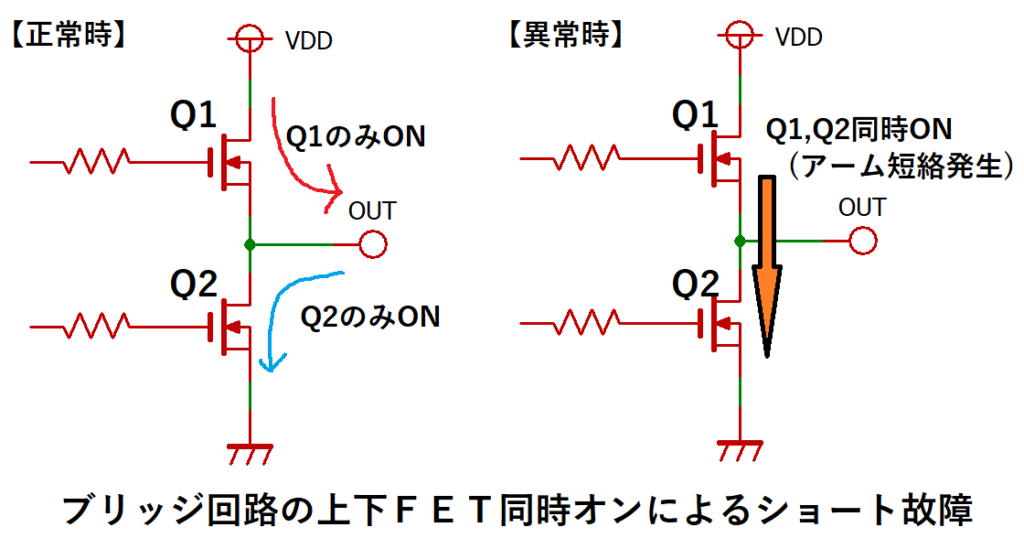

・ブリッジ回路の場合、上下のFETが同時オンを起こしてショート故障する。

スイッチングが遅いと本来片方だけONする動作が、

上下ともONする場合が発生(アーム短絡)して、過電流で壊れる場合があります。

と言う訳で、立上り時間tを決めるのが難しく感じられると思いますが、

一般的な回路のRGは数10 ~ 数100Ωの範囲で用いられているので、

その範囲内で、まず動作させてみて調整を行うのが望ましいです。

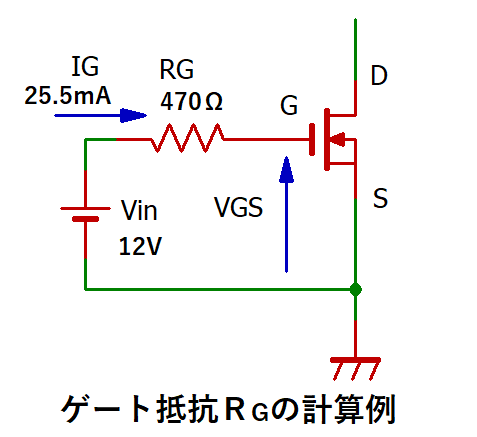

FETのゲート抵抗 計算例

Vin=12Vで東芝製FET TK12A60W を使用する場合

先程提示したダイナミック入出力特性グラフより、

VGS=12V時のQg=30nC となります。

VGSの立上り時間t=1us(=1000ns)とすると、

ゲート電流IGは(1)式より

IG = Qg / t=30 / 1000=0.03 ( = 30mA)

よって、ゲート抵抗RGは(2)式より

RG=Vin/IG =12/0.03=400Ω → 470Ωを選択

実際には400Ωの抵抗値は販売されてないので、抵抗値のラインアップで最も近い470Ωにします。

抵抗値のラインアップ: 一般的にE12系列、E24系列があります。詳しくは「抵抗 系列」で検索してください。

RG=470Ωの場合のゲート電流IGは(1),(2)式を変形して

IG = Vin / RG = 12V / 470Ω ≒ 25.5mA

立上り時間tは

t=Qg/IG=30nC / 25.5mA ≒ 1.17 us

となります。

このゲート電流IGを流しても前段のFET制御回路の電流供給能力に問題がなく、

また、ブリッジ回路で使用する場合は、この立上り時間tで上下ショートする恐れがない

十分なデットタイムをとっているならば使用することができます。

※デットタイム:上下FETが両方ともOFFの期間。

<FETの選定方法や、トランジスタのベース抵抗の決め方等について解説しています>

<FETの安全動作領域(SOA)の判定方法を解説しています>

<FETのスイッチング損失の計算方法について解説しています>

以下の記事で、電子回路工作で役立つ工具類を紹介しています。