この記事でわかること

・同期整流の動作原理と特徴

・同期整流のメリットとデメリット

・同期整流回路を設計する際の注意

・同期整流FETの選び方

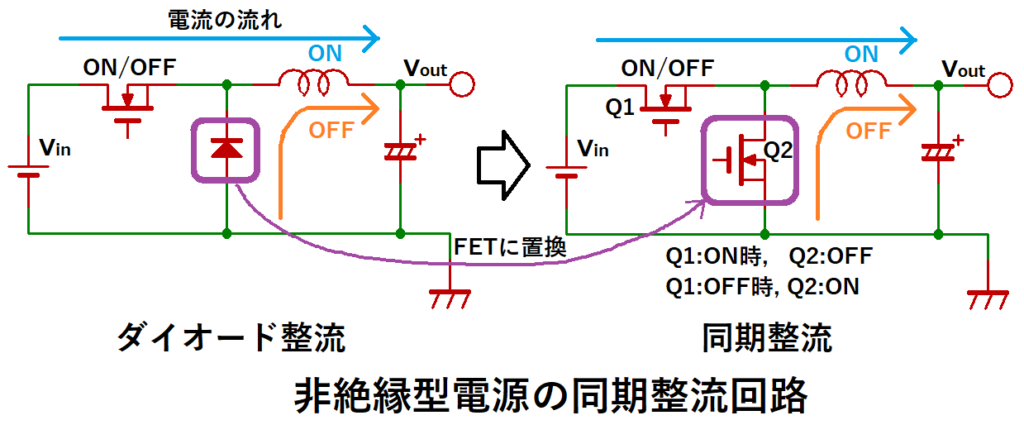

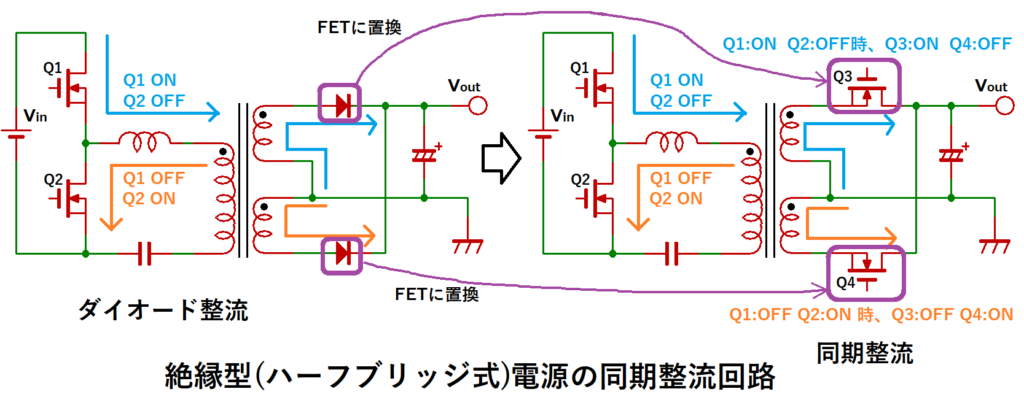

同期整流は、スイッチング電源の出力回路に用いられるダイオードを

FETに置き換えることで、損失を大きく低減できます。

この時、同期整流FETをONさせるタイミングを

電源回路のスイッチング動作と同期させることで、

ダイオードが行っていた整流動作をFETが行います。

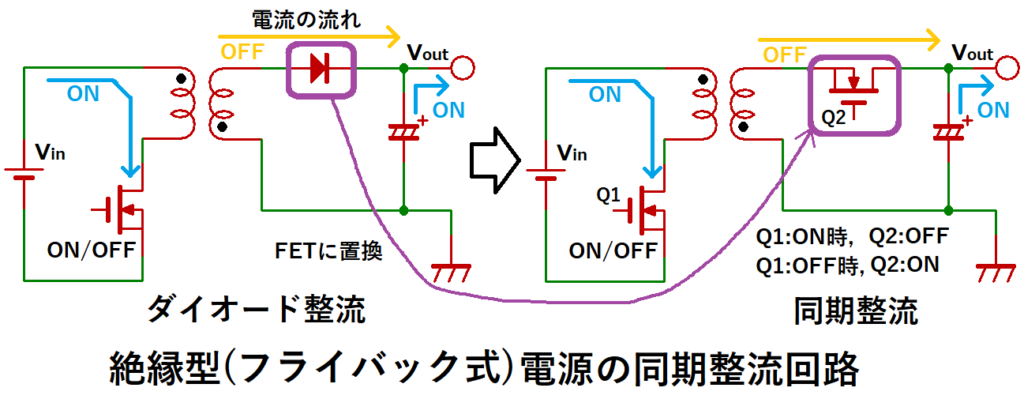

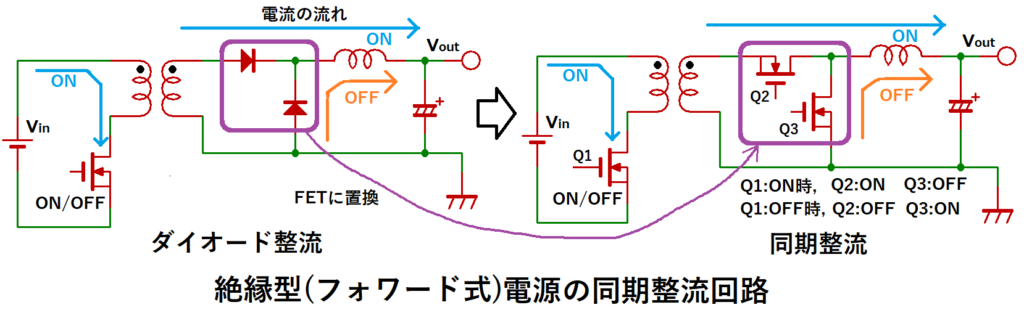

スイッチング電源は様々な回路方式があるため、

同期整流回路も、その回路方式毎に異なります。

本記事では、各種同期整流回路を紹介すると共に、

動作原理を実測波形を用いて、分かりやすく解説します。

また、設計時の注意点や同期整流に使うFETの選び方についても説明します。

同期整流回路の種類と特徴

同期整流は「ダイオードをFETに置き換えたもの」と一言で言っても、

それを適用するスイッチング電源は様々な回路方式があるため、

同期整流回路も、その回路方式毎に異なります。

どの同期整流回路でも共通する事は、

FETに流れる電流の向きがソース(S)→ドレイン(D)となり、

通常FETを使用する時の電流方向(D→S)とは逆になることです。

もちろん、FETがONすれば、ドレイン(D)からソース(S)に電流を流すことができますが、

ソース端子よりドレイン端子の方が電圧が高い時はONしないようにゲートを制御します。

このように、ドレイン電流を逆方向に流して使用する理由は、

FETがONしていなくても、電流を流せるようにする為です。

FETは、その構造上、ソースからドレイン方向にダイオード成分が存在します。

これをボディーダイオード(寄生ダイオード)と呼びます。

つまり、ソース(S)電圧>ドレイン(D)電圧なら、OFFでも電流が流れます。

この状態は、ダイオード整流回路と同じです。

しかし、ボディダイオードの順方向電圧VFは大きいため、損失(=VF×I)が大きくなります。

東芝製パワーMOSFET TK58A06N1(60V 58A TO-220パッケージ)の場合

順方向電圧VDSF=-1.2V (ソース(S)基準の為、-電圧で表記)

このため、できるだけON期間を長くして、

損失が小さくなるようにゲート電圧を制御する必要があります。

(ダイオードよりFETの方が損失が小さくなる理由は後で説明します)

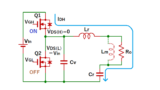

同期整流ICのゲート制御の仕組み

上記で説明した通り、ソース電圧>ドレイン電圧の時に

FETをONするようにゲート制御を行うのが同期整流制御ICです。

(以下、制御ICと称します)

その仕組みについては、各ICメーカーで方法が異なりますが、

基本的には、以下に示す流れで、ドレイン逆電圧を検知し、ゲートをON/OFFさせます。

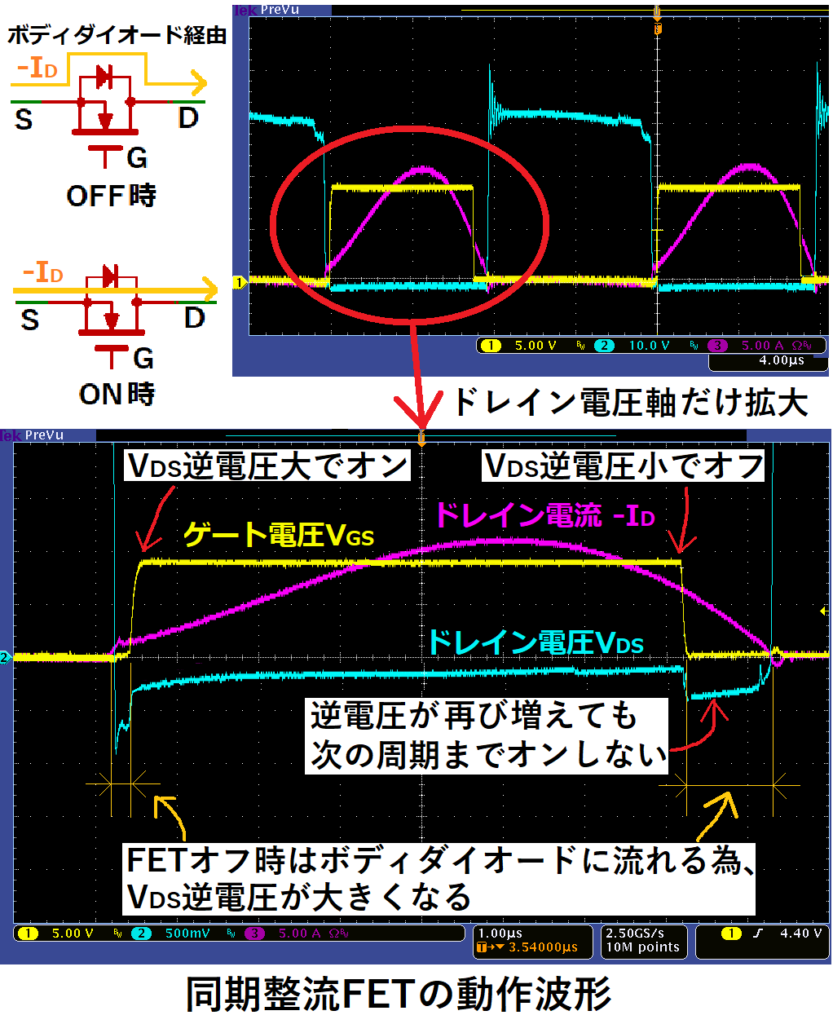

1. 一次側FETのスイッチング動作により、トランスの二次側電圧が上昇すると、

ソース(S)端子の電圧も上昇するので、FETがONしてなくても、

ボディダイオードを経由し、ソース(S)からドレイン(D)方向にドレイン電流-IDが流れます。

(ここでは通常のドレイン電流の流れとは逆なのでマイナス符号をつけています)

2. ドレイン電流-IDが流れることで、ドレイン・ソース間電圧VDSに逆電圧が発生します。

この逆電圧は、ボディダイオードの順方向電圧VFに相当します。

3. VDSの逆電圧が大きくなったら、制御ICはゲート電圧VGSを出力します。

FETがONすると、ドレイン電流-IDはボディダイオードでなく、FET内部を流れます。

<補足>

FETがONすると、ボディダイオードに電流が流れない理由ですが、

ダイオードは順方向電圧VF以上の電圧が印加されないと電流を流すことができません。

FETのオン抵抗Ronは数mΩ程度と非常に小さく、

それによる電圧降下(=Ron×|-ID|)は、

1V程度あるボディダイオードの順方向電圧VFに比べ、非常に小さいです。

例:VF=1V、Ron=5mΩのFETで、電流1Aを流した場合

VF=1V ≫ SーD間の電圧(=Ron×|-ID|=5mΩ×1A)=5mV

このため、ONすると、SーD間電圧はVF以下となるため、ボディダイオードには電流が流れません。

波形を見ても、FETのON期間はVDSの逆電圧が小さくなっていることがわかります。

4. その後、一次側スイッチング動作により、トランスの二次側電圧が下降すると、

ソース端子の電圧も下がるので、ドレイン電流-IDが低下します。

これによって、VDSの逆電圧が小さくなるので、制御ICはゲート電圧VGSを停止します。

FETがOFFすると、ドレイン電流-IDは再びボディダイオードに流れます。

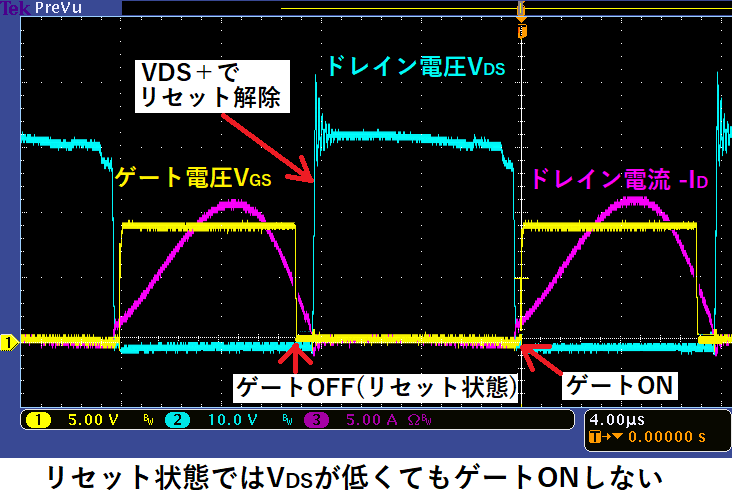

5. ボディダイオード経由になることで、再びVDSの逆電圧が大きくなりますが、

制御ICでは、一度OFFしたらリセット状態にすることで、ONしないようにしています。

リセット状態はVDSの逆電圧が無くなり、+電圧になると解除されます。

これにより、次のスイッチング周期の時にはONできるようになります。

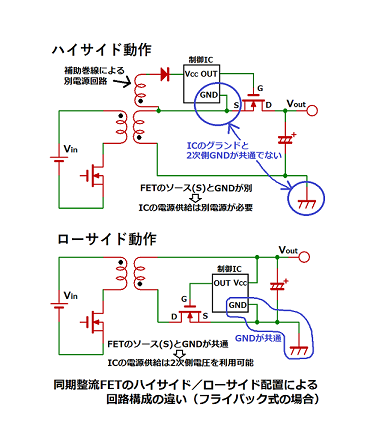

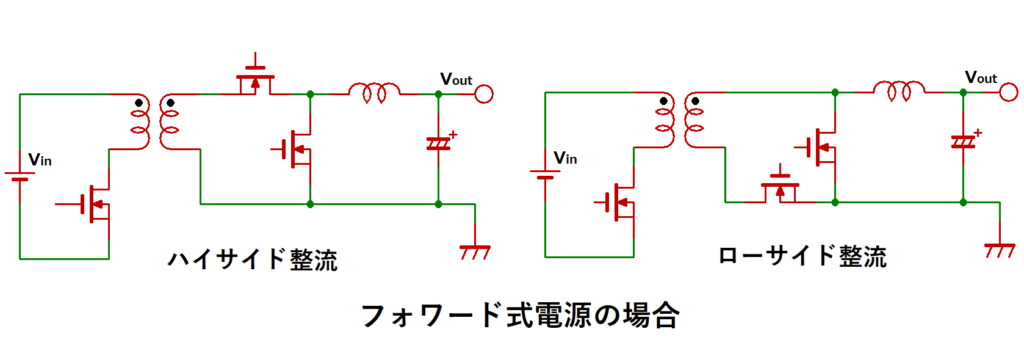

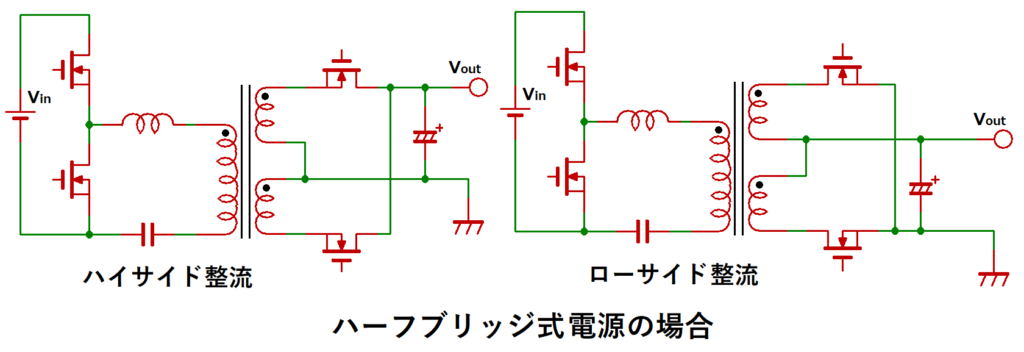

ハイサイド整流とローサイド整流

これまで紹介した同期整流回路のFETは、全てハイサイド(+側)にありましたが、

ローサイド(-側)に配置する方法もあります。

ローサイド側にFETを配置する利点は、

制御IC周辺回路を簡素化できることにあります。

その理由ですが、FETにゲート信号を出力する際、

そのゲート電圧の基準グランドはソース(S)になります。

つまり、同期整流FETのゲート信号を制御するには、

制御ICのグランドをFETのソース(S)に接続する必要があります。

FETがローサイド側ならば、FETのソース(S)と二次側GNDは共通なので、

制御ICへの電源供給は、二次側電圧をそのまま使用できます。

しかし、ハイサイド側の場合、ソース(S)電圧は二次側GNDと共通ではないため、

制御ICに電源供給するには、二次側GNDとは独立した電源回路が必要になります。

具体的には、以下の様な回路を設けます。

・トランス二次側に補助巻線を設け、ソース電圧をグランドにした電源回路を構成する

・ブートストラップ回路を設ける

ブートストラップ回路はハーフブリッジ式電源の

一次側ハイサイドFETのゲート制御にも使用される技術です。

詳しくは下記記事で解説しています。

ローサイド整流にした場合、別電源は不要ですが、

-側ラインでスイッチング動作を行うため、

二次側グランドにノイズが発生してしまう欠点があります。

グランドにノイズが乗ると、周辺回路の動作にも影響する為、

別電源を設けてでも、ハイサイド整流を採用する場合もあります。

同期整流のメリット、デメリット

<メリット>

同期整流のメリットは、

ダイオード整流に比べ損失をなかり小さくできる事です。

どの程度、損失を低減できるか具体例を上げて説明します。

・ダイオード整流の場合

ダイオードに電流Iが流れた時、

順方向電圧VFによる損失(P=VF × I)が発生します。

このため、整流回路にはVFが小さいショットキーダイオードが使われます。

新電元工業製ショットキーダイオードSG20SC4M(40V 20A TO-220パッケージ)の場合、

データシートより、10A時の順方向電圧VF=0.52V(max)なので、

損失Pは、

P=0.52[V] × 10[A]=5.2[W]

となります。

・同期整流の場合

同期整流の損失はFETのON抵抗で決まります。

厳密にはFETのターンON/OFF時の損失、ボディダイオード経由時の損失、

制御ICの消費電流による損失もあります。

東芝製パワーMOSFET TK58A06N1(60V 58A TO-220パッケージ)の場合、

データシートより、10A時のON抵抗Ron=5.4mΩ(max)なので、

損失Pは、

P=5.4[mΩ] × 10[A]2 =0.54[W]

となり、ダイオードの1/10程度に減らすことができます。

<デメリット>

・ノイズが大きい

一次側FETのスイッチングに加え、二次側でもスイッチング動作を行う為、

ダイオード整流に比べ、ノイズが増加します。

特にローサイド整流にした場合はGNDノイズも増えるため、注意が必要です。

・軽負荷時に効率が悪化する

制御ICは、ドレイン逆電圧を検知してゲートをONさせる為、

軽負荷時はドレイン電流-IDが小さいため、VDSの逆電圧が小さくなる事で、

ゲートONできなかったり、できても直ぐにOFFしてしまうと、

ボディダイオードに流れる時間が増加し、損失が増大します。

・コストがかかる

一般的にダイオードよりFETの方が価格が高く、制御ICも必要です。

ハイサイド整流なら、更に別電源回路のコストが加わります。

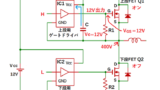

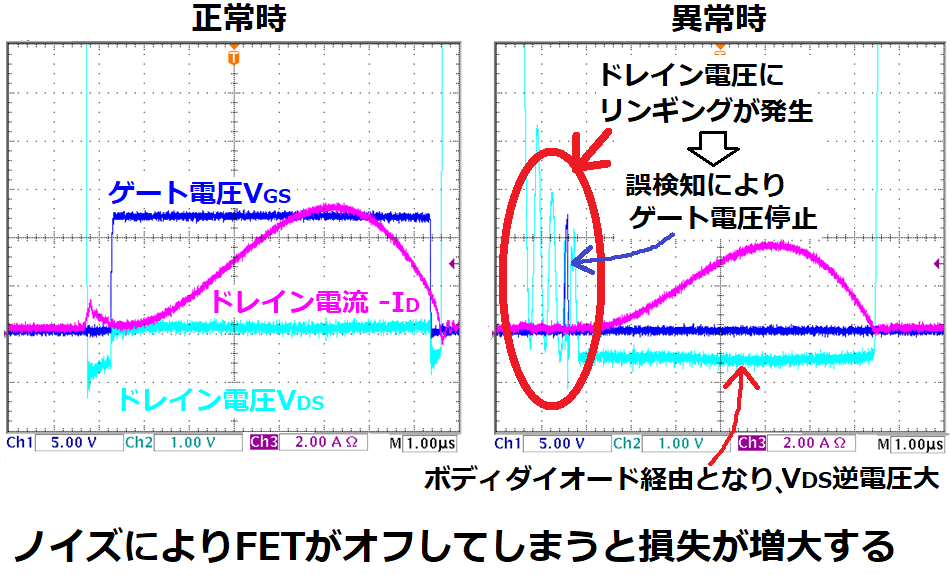

同期整流回路設計の注意点

ゲート制御を行う制御ICは、ドレイン(D)端子の僅かなマイナス電圧(-1V以下)を検出して、

ON/OFFを行うため、ドレイン電圧VDSにノイズが入ると、同期整流動作に影響が出ます。

一次側FETのスイッチング動作により、トランスの二次側電圧の上昇直後は、

トランスの漏れインダクタンス(※1)が原因で、ドレイン電圧VDSにリンギングが発生します。

※1:リーケージインダクタンスとも呼びます。

トランスの巻線部分から磁束が漏れる(漏れ磁束)ことで、

変圧作用をせずに、独立したコイルとして作用するインダクタンス成分です。

「漏れ」という言葉から、悪いイメージがありますが、

電流共振回路(LLC)では、この漏れインダクタンスを利用し、

ノイズの少ないソフトスイッチング動作を行っています。

電流共振回路については下記で解説しています。

このリンギングによって、ドレイン電圧が+側に変動することで、

制御ICが誤検知して、ゲートOFFしてしまうと、

ボディダイオードだけで電流を流すことになります。

これによって、損失が非常に大きくなり、

場合によっては発熱でFETが故障する場合もあります。

制御ICでは、ノイズで誤検知しないように、

ゲートOFFするドレイン電圧の判定値(しきい値)を調整する機能を持つものもあります。

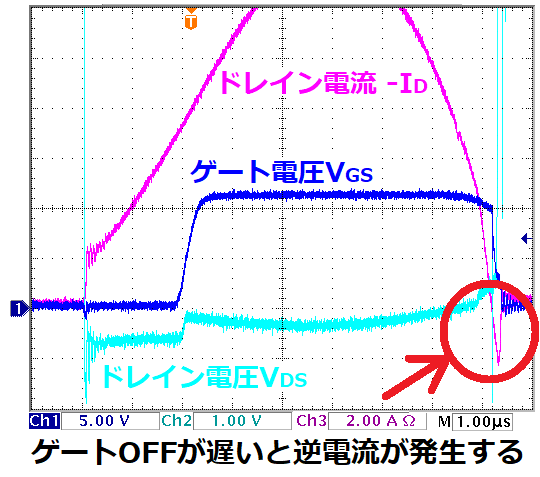

しかし、しきい値を上げると、ゲートOFFのタイミングが遅れるため、

ドレイン電圧>ソース電圧になっても、ONしたままだと、

ドレインからソース方向に逆電流が流れてしまいます。

逆電流が流れると、出力電流の流れを妨げてしまう為、

これも損失を増大させる原因になります。

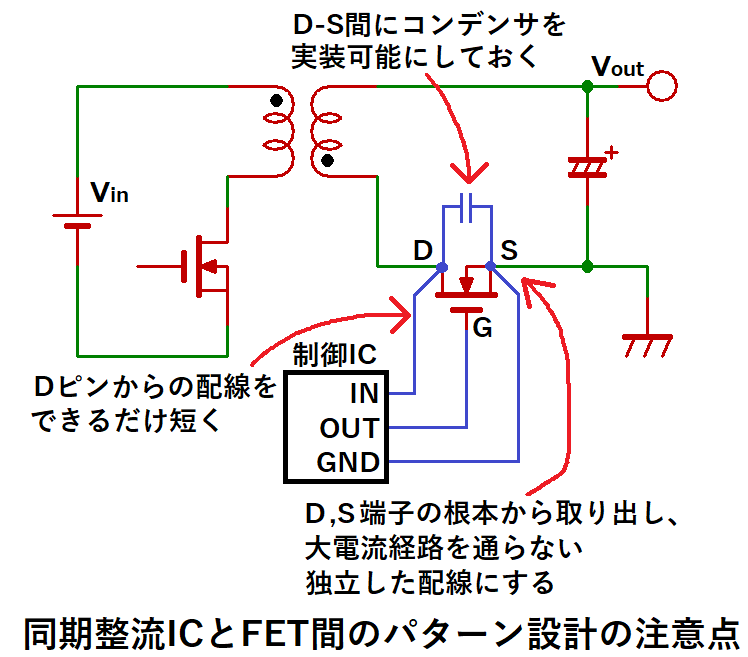

このため、ノイズの影響を受けにくいパターン配線にする必要があります。

具体的には、制御ICをパワーラインから離したり、

ドレイン検出線を最短経路にする等の対策があります。

(D-S間にコンデンサを追加できるようにする理由は後で解説します)

しかし、基板サイズ、部品配置等の制約から、理想配線にするのは難しく、

実験回路では正常動作でも、基板化したら問題が起こることは珍しく無いです。

以上の事から、

同期整流回路の安定動作はパターン設計にかかっていると言っても過言ではありません。

同期整流FETの選定について

同期整流FETの選び方ですが、

使用する制御ICのメーカーで推奨するFETを使用する事をお勧めします。

理由は、安定したゲート制御を行うには、制御ICとの相性が重要だからです。

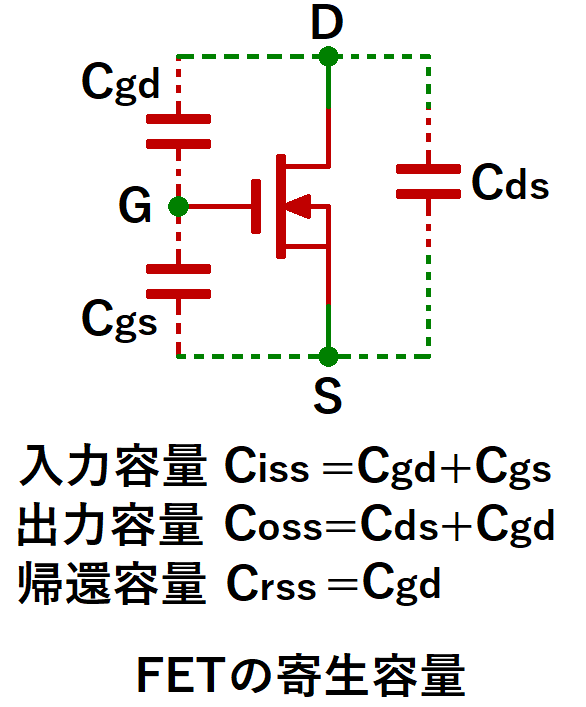

ここで言う相性というのは、FETの寄生容量やボディダイオードの順方向電圧などです。

これらの値によって、ドレイン電圧VDSやドレイン電流-IDの波形が変化し、

ON/OFF制御に影響を及ぼします。

コストや入手性等の問題で、推奨品を採用できないとしても、

試作や初期評価では、推奨品を使って試験し、

まずは正常動作ができるか確認します。

確認する内容としては、以下になります。

・負荷(出力電流)を変化させてもゲートONできているか?

・ゲートONの期間は適切か?(短いと損失が増大し、異常発熱する)

・ゲートOFFが遅れて逆電流が発生していないか?

・出力電圧や、GNDに発生するノイズは問題ないか?

・消費電力(効率)を測定する

(FET置換え後の比較に使用するので、回路全体の電力計測でOK)

正常動作できたら、使用したいFETに置き換え、

その差異を見ながら、調整を行います。

推奨品以外を選定する際は、

まずは、設計する電源回路の出力(電圧・電流)条件を満足する必要があります。

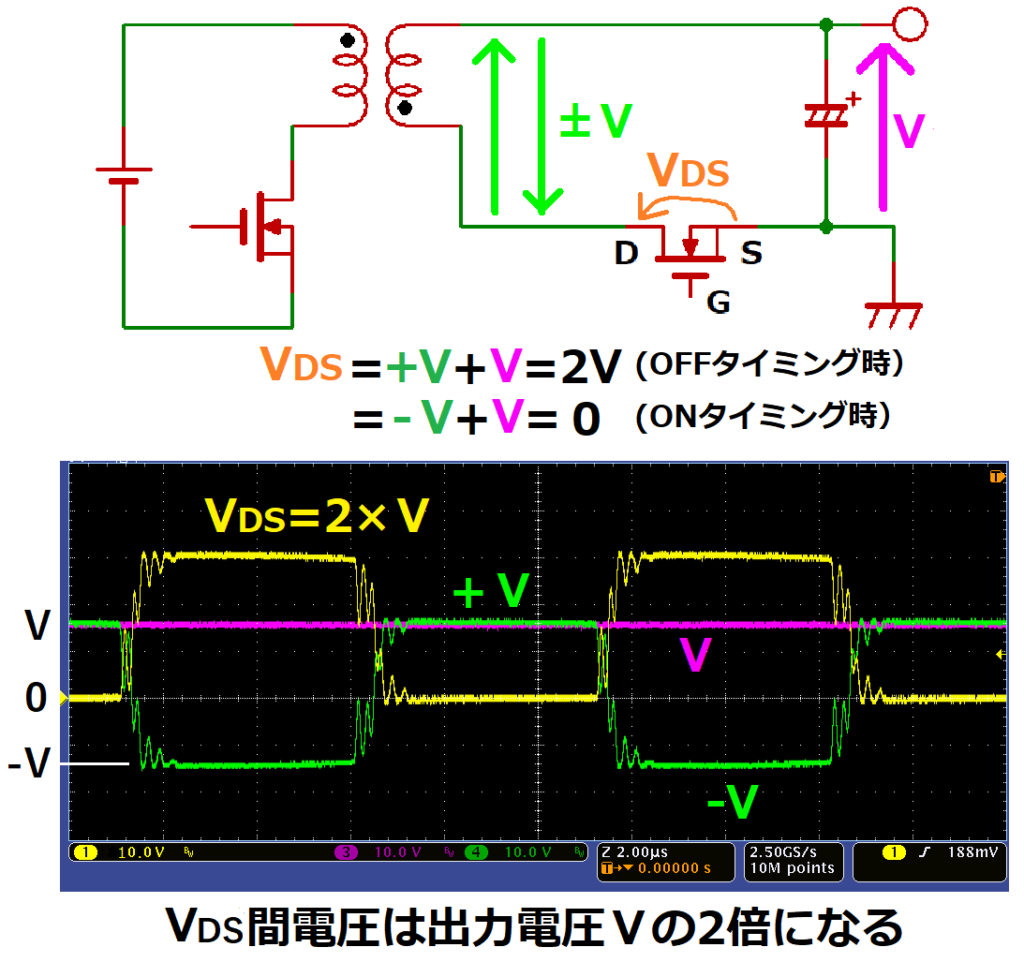

ここで、気を付けるのが、ドレイン・ソース間電圧VDSは

電源回路の出力電圧Voutの2倍の電圧が印加されるため、

VDSの最大定格はVoutの3倍以上あるものにします。

この図では、フライバック式を例にしていますが、

本記事で紹介した絶縁型電源回路すべてに該当します。

(ハイサイド、ローサイド整流両方とも)

ちなみに、出力電圧の2倍の電圧が印加されるのは、

同期整流に限った話ではなく、ダイオード整流でも、耐圧は3倍以上確保します。

その他の選定ポイントとしては、

低損失化が目的なので、ON抵抗が小さい方が良いのはもちろんですが、

ドレインーソース間容量Cdsが小さいとリンギングが大きくなるので注意が必要です。

Cdsはデータシートの出力容量Cossと帰還容量Crssから求まります。

Cds=出力容量Coss ー 帰還容量Crss

Cdsが小さいと、ON/OFF時のCdsへの充放電電流が小さい為、

VDSの立下り/立上りが早くなることで、ON/OFF切替を早くできますが、

VDSの急峻な変化はリンギングの発生を引き起こします。

もし、リンギングが大きく、ゲートOFFしてしまう場合には

D-S間に数百pF程度のセラミックコンデンサを入れてみます。

(コンデンサの耐圧はFET選定と同様、出力電圧の3倍以上にします)

コンデンサ追加により、Cdsの容量が大きくなると

VDSの立下り/立上りが緩やかになり、

リンギングの発生を抑制できます。

また、Cdsが充電される事で、

VDSの逆電圧が大きくなる為、ゲートON検知しやすくなり、

また、ノイズで多少VDSが上昇しても、誤検知によるゲートOFFが起きにくくなります。

★トランジスタやFETの設計方法についてのまとめ記事です。

★基板の部品交換や修正で役立つ工具類を紹介しています。