この記事でわかること

・MCP4921/4922の特徴と使い方

・マイコンとの接続方法

・±出力化などの応用回路例

マイクロチップ製DAコンバータ(以下、DACと称す)MCP4921/4922は

発売から15年以上経過している定番ICの一つです。

このDACはDIPパッケージ品があり、

通販サイトで購入できることから、電子工作等に使いやすいです。

本記事では、MCP4921/4922の使い方を説明すると共に

マイコンとの接続方法や応用回路例について解説します。

<注意点>

本記事は2023年時点でのデータシートを基に作成しています。

使用の際は、最新のデータシートを必ず確認して下さい。

MCP4922の特徴

MCP4921/4922の特徴は以下になります。

・分解能12bit

12bitの2進数の最大値を10進数で表すと(1111 1111 1111)=4095です。

つまり、12bitで、0~4095の4096個の値を表現できるので、

本DACは出力電圧を4096分割できます。

(4096=212なので、nビットの分解能を持つことは2n分割できることを意味する)

例えば、DACの最大出力電圧を4Vにした場合、

4[V]/4096≒0.001[V]

となり、1mV単位で出力電圧を変化できます。

この電圧変化の最小単位は、デジタル入力が2進数表記において、

右端の最下位ビットが変化した時になります。

例: (000……000) → (000……001)

この最下位ビットをLSB(least significant bit える・えす・びー)と呼び、

DACの性能を規定する上での基準単位として使われます。

先程の例だと、1LSB=1mVになります。

・出力精度

DNL:±0.75LSB

INL:±12LSB

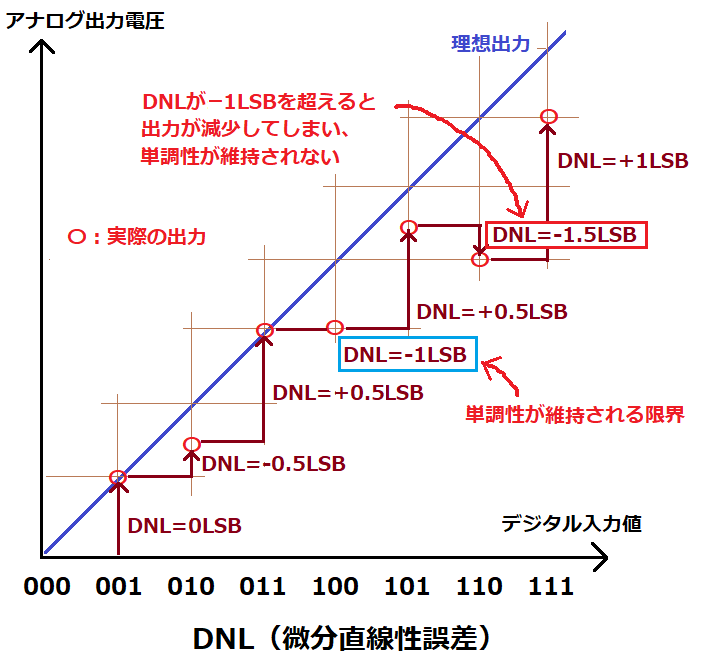

DNLは微分直線性誤差(Differential Non-Linerarity)です。

これは、デジタル入力が1bit変化した時に、

アナログ出力電圧の理想変化量との差になります。

理想的には1bit変化すると、出力電圧は1LSB分変化するので、

先程の例に当てはめると、1LSB=1mV変化します。

しかし、実際の変化量は、ばらつきが存在し、このDACの場合、

理想値である1mVの変化に対し、±0.75LSBの誤差が発生します。

つまり、±0.75mV余分に変化するので、1bit変化したら±1.75mV変化します。

もし、DNLが±1LSBより大きいと、1bit変化で出力電圧が2LSB以上変化するため、

デジタル入力が1bit増加時に、出力電圧が低下してしまう場合が発生してしまい、

デジタル入力と出力電圧の比例関係(単調性)を維持できなくなります。

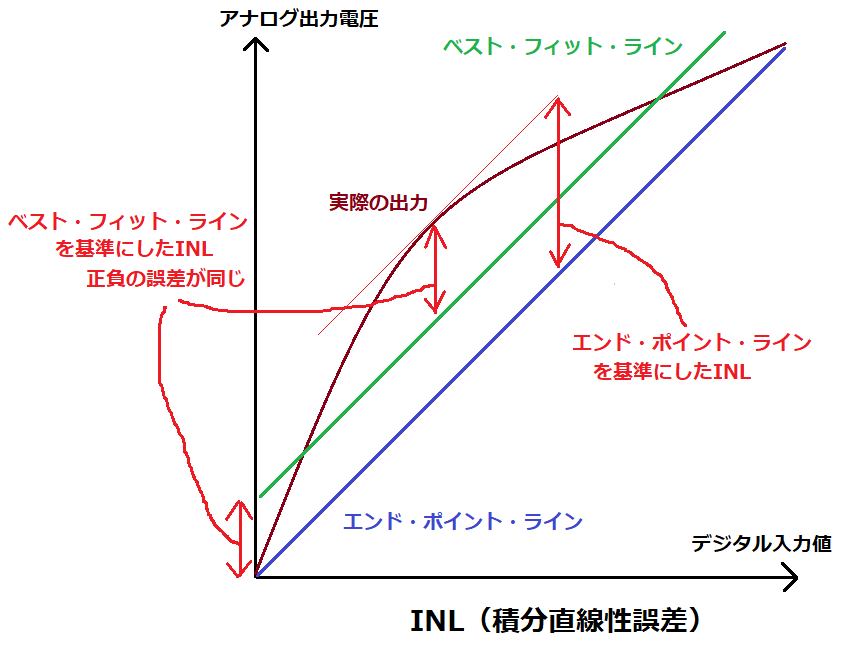

INLは積分直線性誤差(Integral Non-Linerarity)です。

これは、DNLによる1bitづつの誤差の積み重ねによって、

誤差が段々と広がっていった時の理想電圧値と実電圧値の最大差になります。

理想電圧値の定義については2種類あります。

・エンド・ポイント・ライン

デジタル入力が0から最大値までを結ぶ直線を基準

本DACが採用している基準であり、

一般的にはこちらを使用してDNLを規定しているDACが多いです。

・ベスト・フィット・ライン

実電圧値との±誤差の最大値が等しくなる直線を基準

こちらの基準だと、INL値が見かけ上、小さくなるため、

DAC選定の際は、どちらの基準を使用しているか注意する必要があります。

本DACのINLは±12LSBなので、最大値を4Vとした時、1LSB=1mVなので、

最大±12mVの誤差が発生することになります。

以上から、INLはミクロ的な誤差、DNLはマクロ的な誤差と考えることができます。

本DACのDNL=±0.75LSB、INL=±12LSBは精度が良い方なのか?についてですが、

DNLやINLが0.1LSB以下の精度を持つDACがある為、

超高精度タイプではありませんが、十数mV程度の誤差なら、

汎用DACとしては十分な精度と言えます。

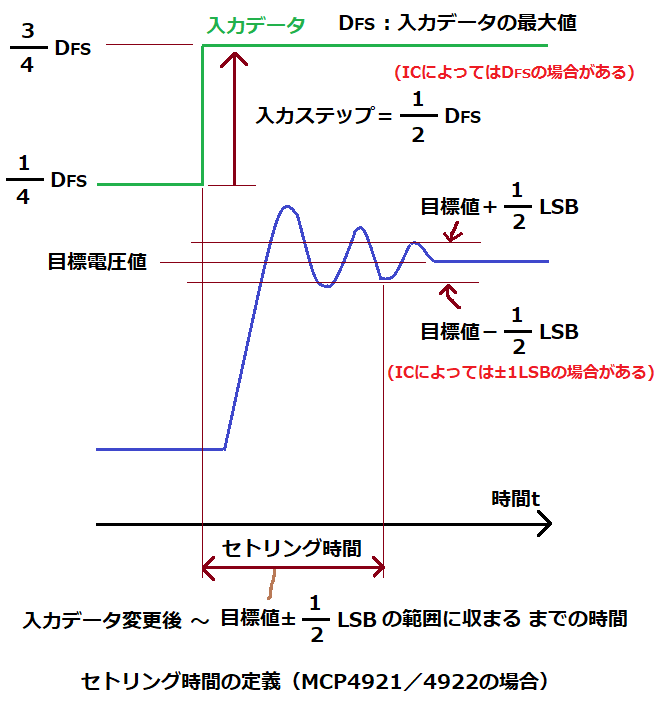

・セトリング時間 4.5μs

この時間は入力が変化した時に出力が安定するまでの時間です。

入力変化量の条件については、0から最大値までのフルスケールの場合と、

フルスケールの1/2の場合があります。

出力安定の範囲については、目標値の±LSB/2と±1LSBの場合があります。

本DACのデータシートでは、

入力がフルスケールの1/4から3/4に変化した時と記載されているので、

フルスケールの1/2の変化量で規定されており、

出力が±LSB/2に収まるまでの時間としています。

同じマイクロチップ社のDACが6~16us程度なので、4.5usは早い方です。

(電流出力型DACにはセトリング時間がnsレベルのものがあります)

電流出力型DACについては下記記事で解説しています。

・入力方式 SPI 20MHz

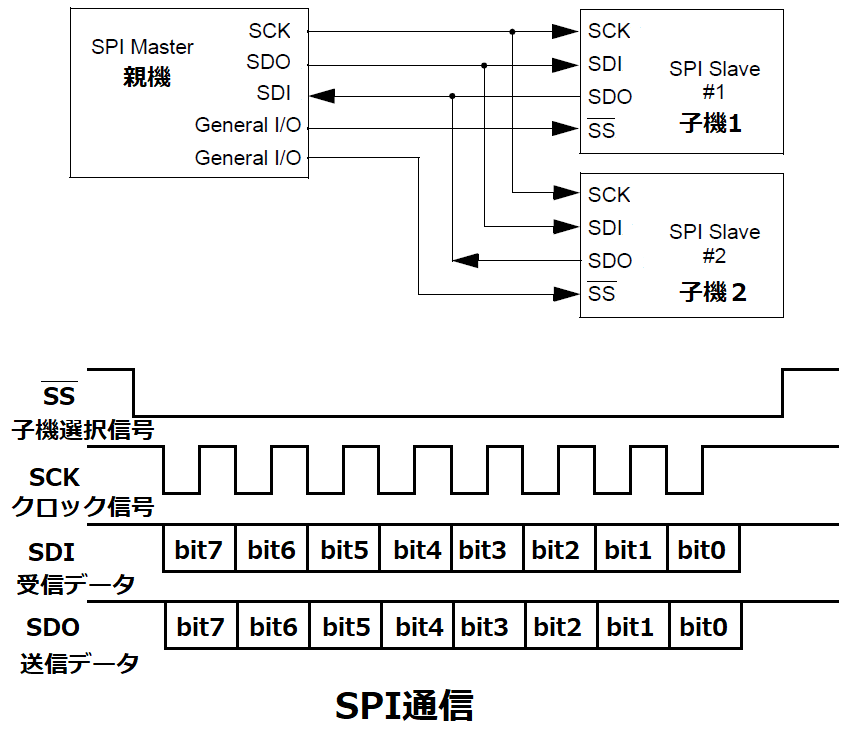

SPI(エスピーアイ)とは、シリアル・ペリフェラル・インターフェイスの略で、

ペリフェラル(周辺機器)との同期式シリアル通信方式になります。

SPIは、マスター(親機)から出力されるクロック信号(SCK)に同期して、

スレーブ(子機)に対し、送信データ(SDO)、受信データ(SDI)をやりとりします。

(DACは子機となり、受信のみ行うため、SDO端子はありません)

子機は複数接続できるため、

親機から各子機に個別に入力されるスレーブ選択信号(SS※1)がLの時、

子機は自分宛であることを認識します。

(※1:本DACではチップ選択信号(CS)と呼ばれています)

一般的なSPI通信の最大クロック周波数が50MHz程度なので、20MHzは比較的早い方です。

このクロック周波数で入力データ受信完了までの時間が決まります。

先程のセトリング時間は入力データを受信完了してからの時間なので、

この通信時間もDACの処理速度に影響します。

他のシリアル入力方式でI2C(アイ・ツー・シー)通信を持つDACもあり、

SPIより低速ですが通信線が2本で済みます。

・アナログ出力点数 2ch

MCP4922はアナログ出力が2つあり、入力データ内で、どちらに出力するか指定します。

MCP4921は出力が1chで、4922にはあるスタンバイモードへの切替ピンが省略されています。

(切替は入力データで指定)

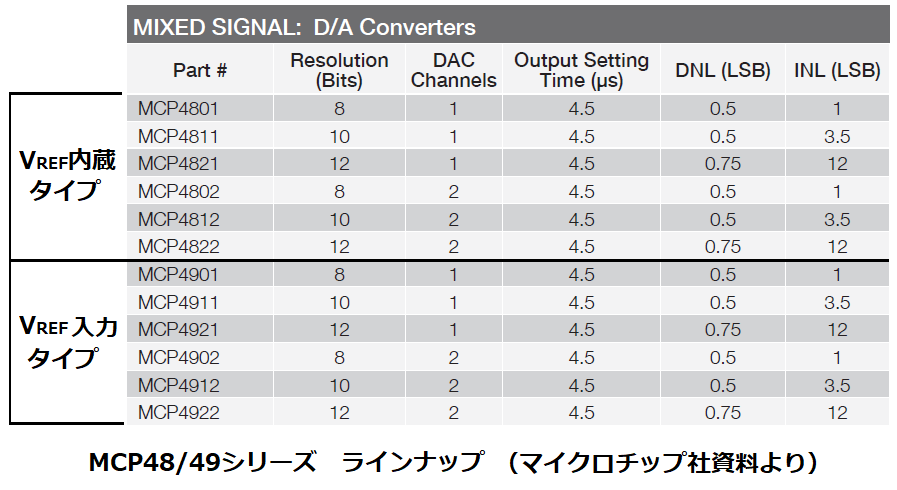

この他にも、以下のラインナップがあり、分解能が8、10bitタイプも存在します。

ここで、VREF内蔵とあるのは、2.048Vの基準電圧源が内蔵されているもので、

外部からの基準電圧入力が不要になります。

(2.048Vという中途半端な値である理由は後で説明します)

分解能が8bitなどの低い方が、INLが小さくなります。

理由は本DACが抵抗ストリング型であることに起因しています。

(この後の「抵抗ストリング型DAC」の解説を参照)

ただし、MCP4921/4922以外の入手性はあまり良くないです。

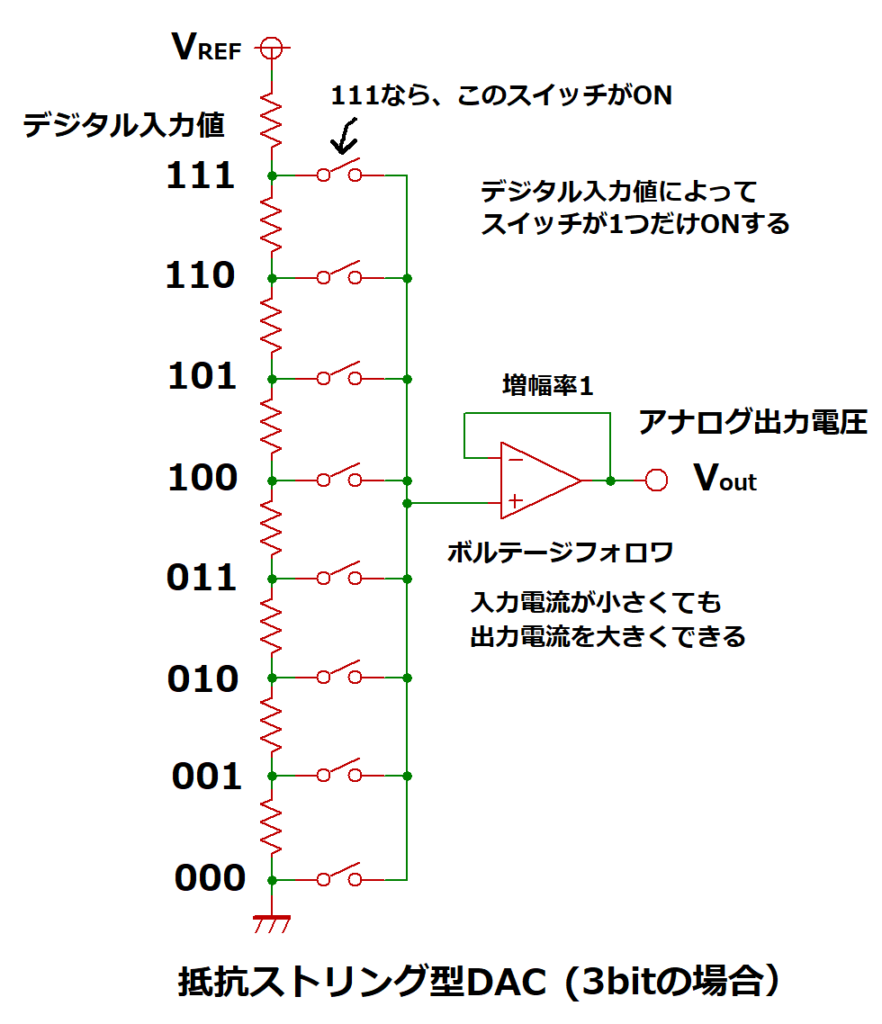

抵抗ストリング型DAC

本DACが採用しているDA変換方式です。

抵抗ストリング(抵抗列)は、

図の様に抵抗を一列に接続することで、基準電圧VREFを分圧し、

スイッチで一箇所を選択することでアナログ電圧を出力する方法です。

デジタル入力が1増えれば、一段上のスイッチに切替わるので、

アナログ出力電圧が抵抗1個分、上昇します。

この回路構成は、抵抗値の精度が悪くても、

デジタル入力の増加に対して、出力電圧が必ず上昇するので、

単調増加性が保証されています。(DNLを低く抑えられる)

使用する抵抗とスイッチの数ですが、

図の様にデジタル入力が3bitの場合、アナログ出力は23=8段階にわかれます。

このため、抵抗とスイッチを8個使用します。

つまり、ビット数nに対して、2n個の抵抗とスイッチが必要になるので、

5bitで25=32個、12bitだと212=4096個と指数関数的に増えていきます。

抵抗の数が増えると、各抵抗値のばらつきの影響が大きくなり、

理想電圧との差が広がるため、ビット数が増えるほどINLが高くなります。

さらに、スイッチに使われるFETには寄生容量があるため、

スイッチの数が多いと、コンデンサ成分の影響により、

動作速度(セトリング時間)が低下してしまいます。

このため、抵抗ストリング方式はビット数を大きくできないため、高分解能出力には不向きです。

MCP4921/4922の使い方

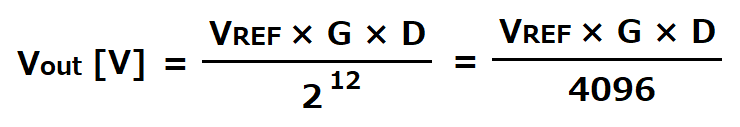

出力電圧の設定

出力電圧は以下の式となります。

VREF:基準電圧

MCP4921の場合はVREFA、MCP4922の場合はVREFAとVREFBピンに電圧を入力します。

AとBでVREFを変えることで、出力VOUTAとVOUTBで電圧範囲を変えることができます。

G:ゲイン(1倍、又は2倍)

初期状態は2倍になっており、

1倍にしたい場合はSPI通信で設定を切り替えます。

D:デジタル入力値(12bit)

マイコン等からSPI通信を介して入力される12bitの2進数です。

Dの最大値は2進数で1が12個の(1111 1111 1111)=4095です。

ゲインG= 2 で、VREF=2.048V にした場合、

最大出力電圧はD=4095の時なので、

VOUT=2.048×2×4095/4096=4.095≒4V

となり、0V ~ 4V のフルスケール出力が得られます。

(但し、電源電圧VDDより高くすることはできません)

また、この時の出力電圧の最小ステップ(1LSB)は

G×VREF/4096=2×2.048/4096=0.001V=1mV

と、ぴったり1mV単位で電圧を設定できます。

先程説明したVREF内蔵タイプの電圧が2.048Vと中途半端な値である理由は、

このように、最小ステップを理想的なきりの良い値にするためです。

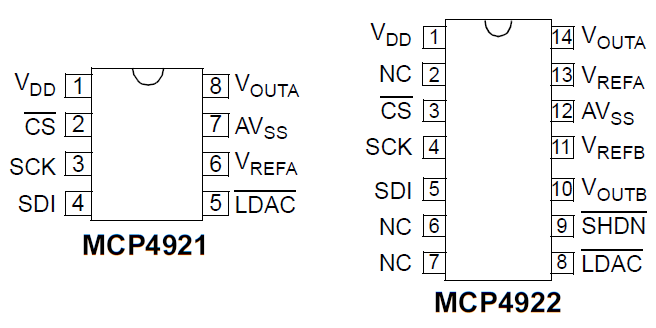

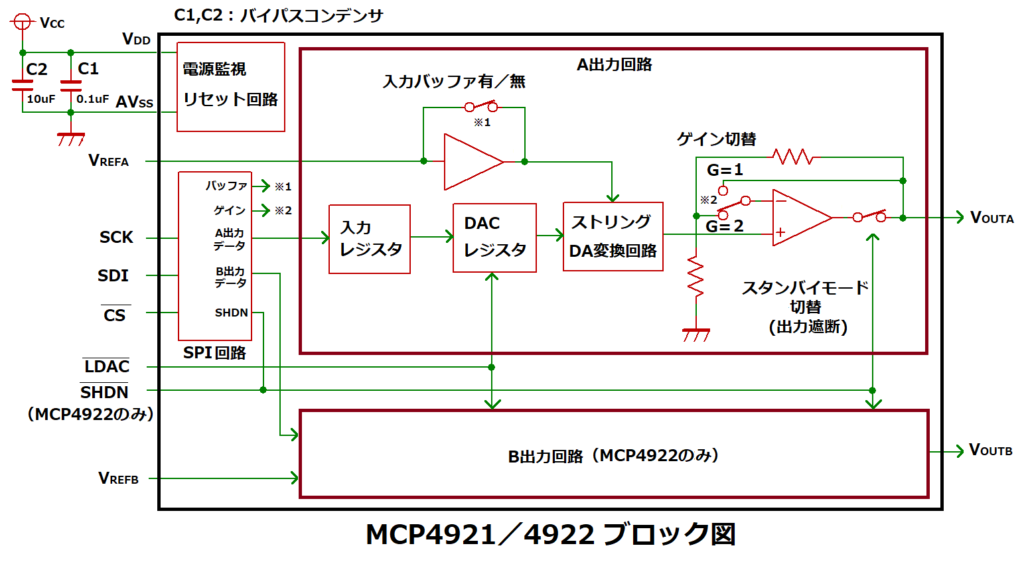

入出力ピン

MCP4921/4922のピン配置とブロック図を以下に示します。

VDD:電源入力(2.7~5.5V)

この電圧によって、各入力信号のH/Lレベルのしきい値が決まります。

Hレベル入力電圧 VIH:0.7 VDD以上

L レベル入力電圧 VIL:0.2 VDD以下

入力はシュミットトリガなので、0.05VDDのヒステリシスを持ちます。

つまり、一度Hレベルになったら、(0.7ー0.05)VDDまで低下してもHレベルを維持し、

一度Lレベルになったら、(0.2+0.05)VDDまで上昇してもLレベルを維持します。

電源安定化のため、VDDピンの直近(4mm以内)にバイパスコンデンサを接続します。

データシートを見ると、

0.1uFのセラミックコンデンサと10uFのタンタルコンデンサを推奨していますが、

タンタルは故障するとショート状態になるため、使用禁止にしているメーカーが多いです。

このため、高容量が必要な場合、電解コンデンサを使うのが一般的ですが、

10uF程度ならセラミックコンデンサもあるので、タンタルを使うのは避けるべきです。

VDDへの電源電圧が低下し、リセット電圧VPOR以下になるとICがリセット状態になります。

(VPORは平均値2Vで定義されており、低下期間が2us以上になるとリセットが発生)

AVSS:アナログGND入力

CS :SPI通信のチップセレクト入力

Lレベルが入力されるとDACがSPI入力を受け付けます。

SCK:SPI通信のクロック入力

SCKの立上りのタイミングでSDI信号のデータを入力します。

SDI:SPI通信のデータ入力

入力されるデータの内容については、

この後の「入力タイミングチャート」で説明します。

LDAC:ラッチ DAC 入力

Lレベルが入力されると、

SDIから受信したデジタル入力値に応じたアナログ電圧を

出力(VOUTA、又はVOUTB)に出力します。

この信号がHレベルの場合、新たなデジタル入力値を受信しても出力に反映せず、

前回の出力電圧を保持します。(初回は0Vを保持)

デジタル入力値を受信したら直ぐに出力に反映させたい場合は、

本入力をLレベルに固定しておくことで、

CSの立上り(データ受信完了)のタイミングで出力されます。

SHDN:シャッドダウン入力(MCP4922 のみ)

Lレベルが入力されると、スタンバイモードになります。

この時、VOUTからの出力は停止して、出力抵抗が約500kΩのハイインピーダンス状態となり、

VOUTピンが外部とつながっていないのと、ほぼ同じ状態になります。

このモードにすることで、DAC未使用時の消費電力を低減できます。

スタンバイモードへの切替はSPI通信からも可能なので、

SHDNピンが無いMCP4921もスタンバイモードにできます。

本入力をHにするか、SPI通信で通常モードに復帰できますが、

復帰時の出力セトリング時間は 10 μs 未満となり、通常動作時の4.5 μsより長くなります。

VREFA、VREFB:基準電圧入力(VREFBはMCP4922 のみ)

VOUTA、VOUTBそれぞれのVREFとなります。

入力できる電圧はVDD以下です。

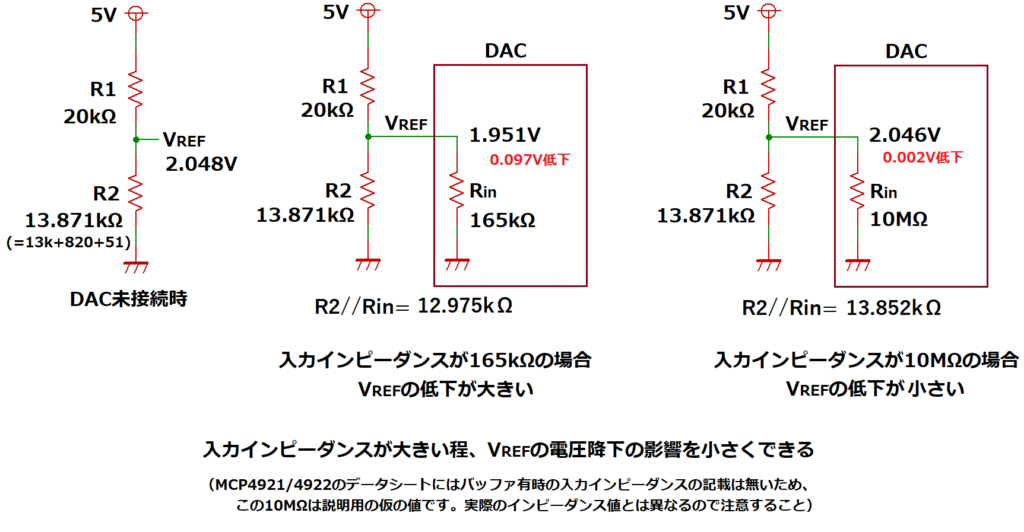

このVREF入力は、バッファアンプ入力に切り替えることができます。

(SPI通信で切替設定ができ、初期状態はバッファ無の設定)

バッファアンプにより、入力インピーダンスを大きくできるため、

VREF端子への入力電流が小さくなることで、VREF電圧変動の影響を小さくできます。

わかりやすく説明すると、図のように、R1とR2でVREFを設定した場合、

入力インピーダンスRinの影響により、

VREFはR2とRinの合成抵抗(R2//Rin)とR1の比で決まるため、

このRinが大きい程、R2//Rinの合成抵抗値がR2と変わらなくなるので、

VREFの低下を小さくできます。

※データシートにはバッファ無時の入力インピーダンスが165kΩとありますが、

バッファ有時については記載が無いので、ここでは仮に10MΩとして計算しています。

但し、バッファアンプ入力にした場合、VREFの入力範囲が0.04V~VDD-0.44Vに狭まります。

VOUTA、VOUTB:アナログ電圧出力(VOUTBはMCP4922 のみ)

2つある出力のうち、どちらに出力するかは、SPI通信で指定します。

ゲインGを2倍にした時は、VREFよりも高い電圧にできますが、

出力できる電圧はVSS~VDDの範囲になります。

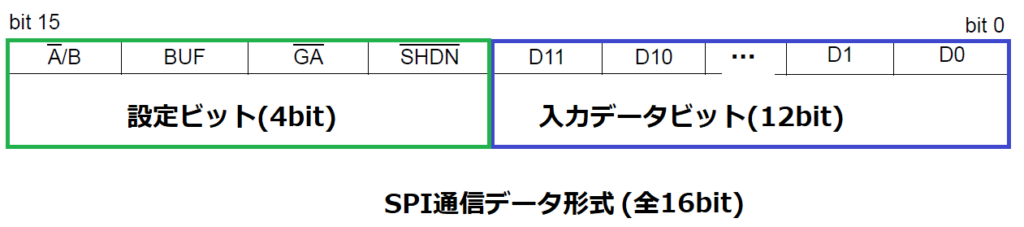

SPI通信データの内容

SDI端子に入力されるデータは16bitで以下の形式となります。

bit 15: A/B : アナログ出力VOUTA、VOUTBどちらに出力するか指定

1 = VOUTB (MCP4922 のみ)

0 = VOUTA

bit 14 :BUF : VREF 入力バッファの有/無を指定

1 = バッファ有

0 = バッファ無

bit 13: GA : 出力ゲインの指定

1 = 1倍

0 = 2倍

bit 12: SHDN : シャットダウン制御の指定

1 = 通常モード

0 =スタンバイモード

bit 11-0: D11~D0 : デジタル入力値(12bit)

2進数で入力、10進数表記で0 ~ 4095の範囲で指定できる

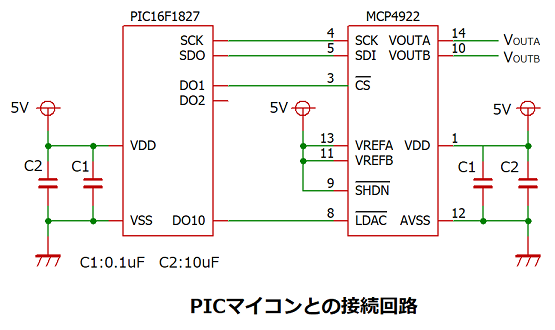

マイコンとの接続方法

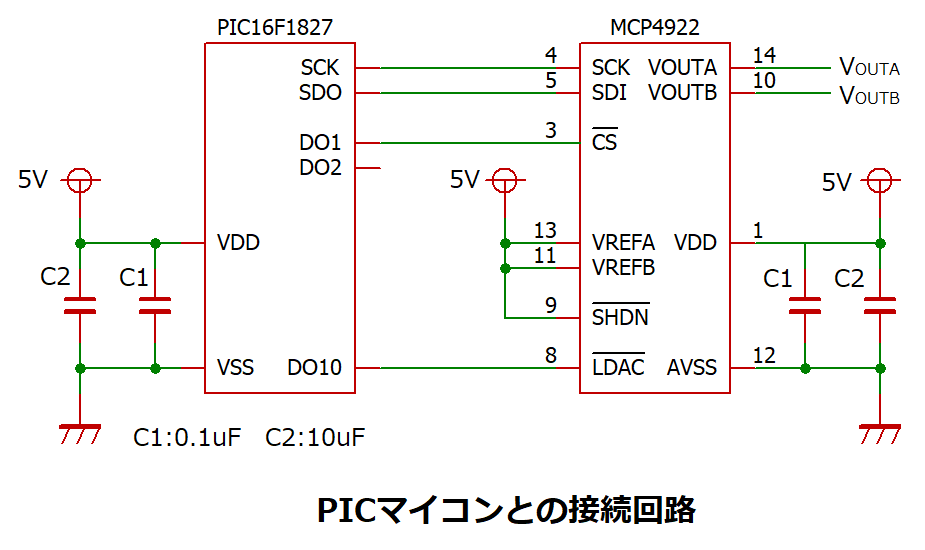

ここではSPIインターフェイスを持つPICマイコン(PIC16F1827など)を例にします。

昔の定番だったPIC16F84AにはSPI通信機能は無いので注意して下さい。

(現在の定番はPIC16F1ファミリです)

PICにもDAコンバータが内蔵されているものがありますが、

高分解能や出力点数を増やしたい場合に外部にDACを接続します。

図のようにPICのSPI通信ピンをDACに接続します。

PIC側 DAC側

SDO → SDI(PICのデータ出力をDACのデータ入力へ)

SCK → SCK(クロック信号)

※DACに送信機能は無く、マイコンからの1方向通信になるので、

PIC側のSDI(データ入力)、SS(セレクト入力)は使用しません。

DACのCSとLDACへの入力は、PICの汎用I/Oを使用します。

(RA0~RA7、RB0~RB7など、PICのピン数によって使用できる汎用I/Oの数は異なる)

この汎用I/Oの中から任意の2点を選び、出力(DO)モードにして接続します。

ここでは選択したDO出力をDO1、DO10とします。

PIC側 DAC側

DO1 → CS

DO10 → LDAC (又はLDACをGND接続)

アナログ出力のタイミングを入力データの送信完了と同時に行う場合は、

LDACをGNDに接続することで、CSの立上りのタイミングで出力されます。

SHDN(シャッドダウン入力(MCP4922 のみ有))については、

DAC未使用時にスタンバイ(低消費電力)モードにする必要がなければ、

VDD(この例では5V)に接続して、通常モード固定にします。

また、2ch出力を持つMCP4922の場合、

VOUTA、VOUTBどちらに出力するかについては送信データ内で指定します。

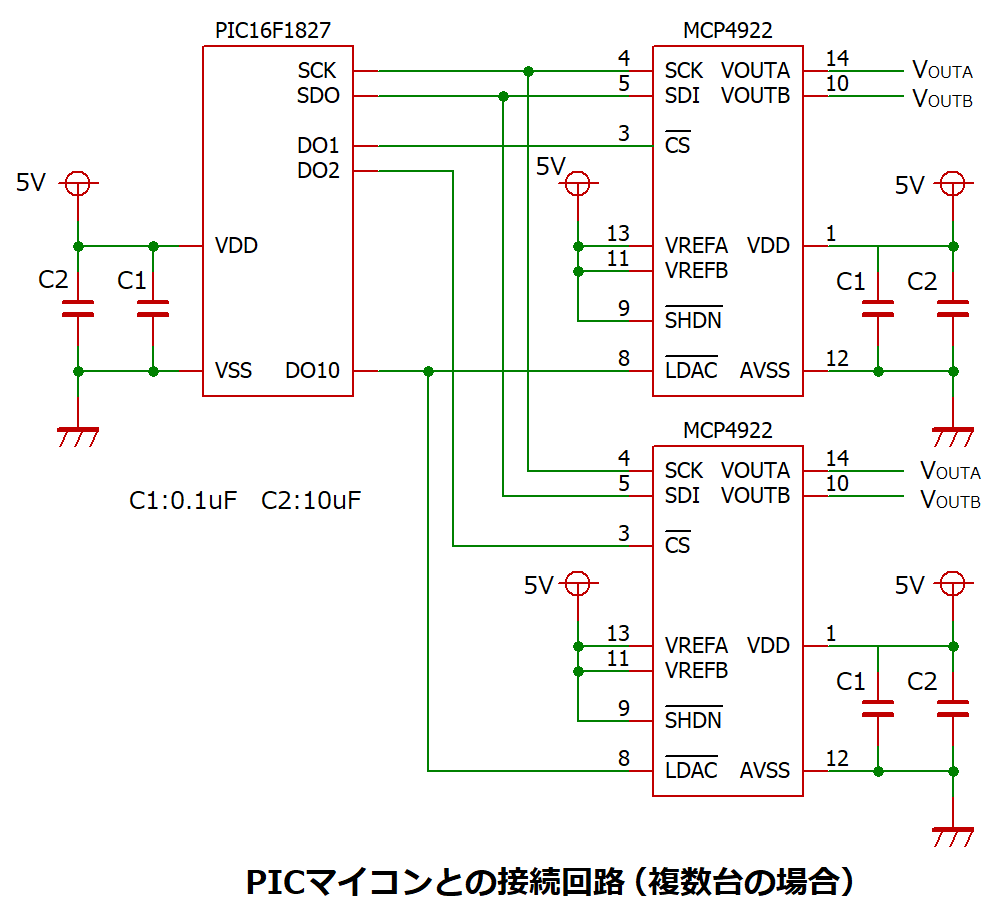

DACを複数台接続する場合は図のようにSDI、SCK、LDACは共通接続にし、

CSはPICのDO1とDO2を使って個別に入力させます。

CSを分けることで、PICから送信されたデジタル入力が、どのDAC宛なのか指定できます。

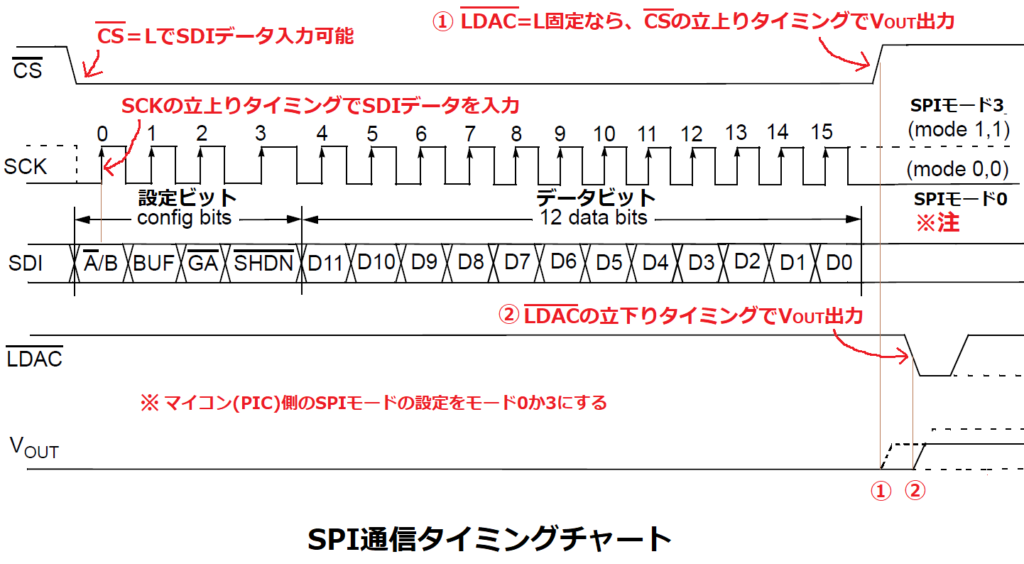

入力タイミングチャート

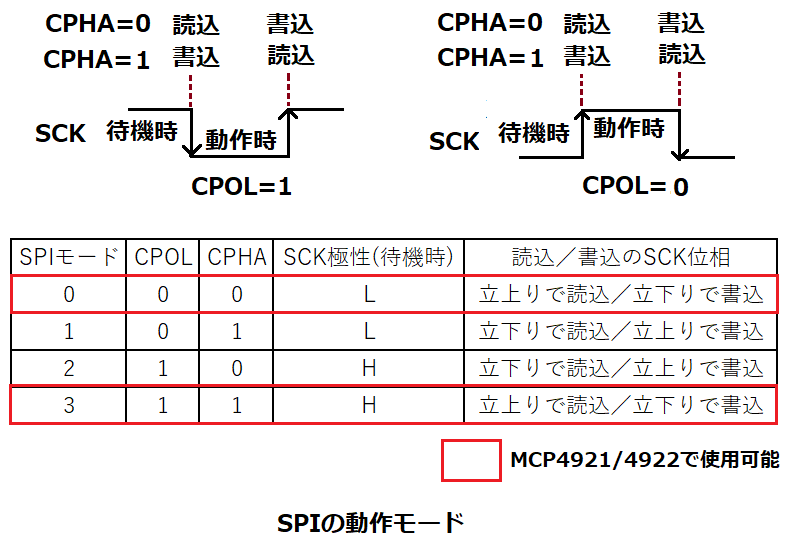

SPI通信を行うにあたり、クロックSCKは、以下の設定を決めておく必要があります。

・SCKの極性

待機時L(CPOL=0)

待機時H(CPOL=1)

・SCKの位相(データの読込、書込タイミング)

最初のエッジでデータを読込み、次のエッジで書込む(CPHA=0)

最初のエッジでデータを書込み、次のエッジで読込む(CPHA=1)

この極性(CPOL)と位相(CPHA)の組合せによって、SPIには4つのモードがあります。

本DACのデータシートにあるタイミングチャートを見ると、

SPIモードがモード0(mode 0,0)か、

モード3(mode 1,1)が使用可能と記載されています。

SPIモードが0又は3という事は、

本DACはSCKの立上り時にデータを読込むことを意味するため、

PIC側ではSCKの立下り時にデータを書込むようにしておく必要があります。

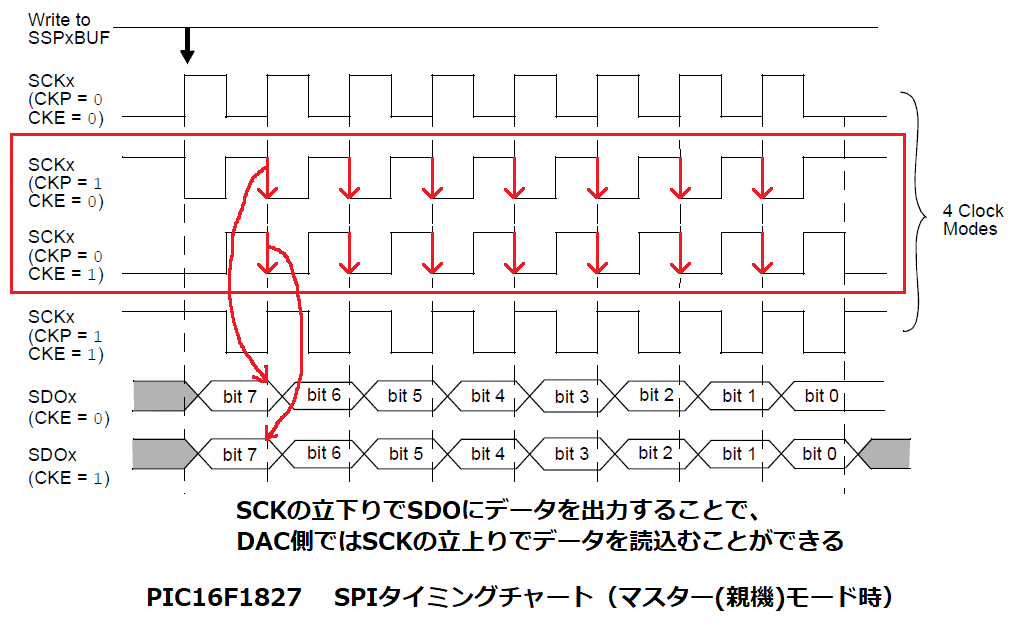

PICマイコンではSPIモードの設定をCKPビットとCKEビットで行います。

SCKの極性

CKP=0:SCKは待機時L、動作時H(アクティブ・ハイ)

CKP=1:SCKは待機時H、動作時L(アクティブ・ロー)

SDOへの出力タイミング

CKE=0:SCKが 待機→動作 に変化した時にデータ出力

CKE=1:SCKが 動作→待機 に変化した時にデータ出力

従って、立下り時にデータを書込むようにするには、

(CKP、CKE)=(0、1)又は(1、0)

に設定します。

PICマイコン側のSPIモードの設定を行った上で、以下の手順でSPI通信を行います。

1.PICのDO1(DACのCS入力)をLにする

SPI通信データが自分(DAC)宛であることを認識します。

2.PICのSDOから通信データ(16bit)をDACのSDIに入力する

3.DACはPICから送信されたSCK(クロック信号)の立上りのタイミングで

SDIのH/Lレベルを読込む

このデータ読込みを16クロック分行います。

4.PICのDO1(DACのCS入力)をHにする

DACはSDI入力データをラッチ(保存)します。

PICのDO10(DACのLDAC入力)の状態によりVOUTの出力タイミングが2通りに分かれます。

①LDAC=L固定の場合

CSがHになったタイミングでVOUTが出力

②LDAC=Hの場合

VOUTは前回の入力データによる出力電圧を保持(初回時は、VOUT=0V)

5.LDAC=Hの場合、LDAC=Lにしたタイミングで、

今回のSDI入力データの値を反映したアナログ電圧をVOUTから出力する

VOUTA、VOUTBどちらに出力するかは、入力データ内のA/Bビットで指定します。

・SCKのクロックが16回終わらないうちにCSがHになった場合、

データ入力は中止(無効)となります。

・SCKのクロックが16回終わってもCSがLのままの場合、

それ以上のクロックが入力されても、データを余分に読込みません。

(17回目以降のクロックを無視する)

MCP4922の応用回路例

データシート等に記載されている応用回路について解説します。

<注意>

抵抗値等の回路定数については、データーシート等から引用したものであり、

動作を保証するものでは無いため、参考程度として下さい。

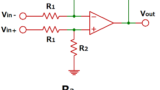

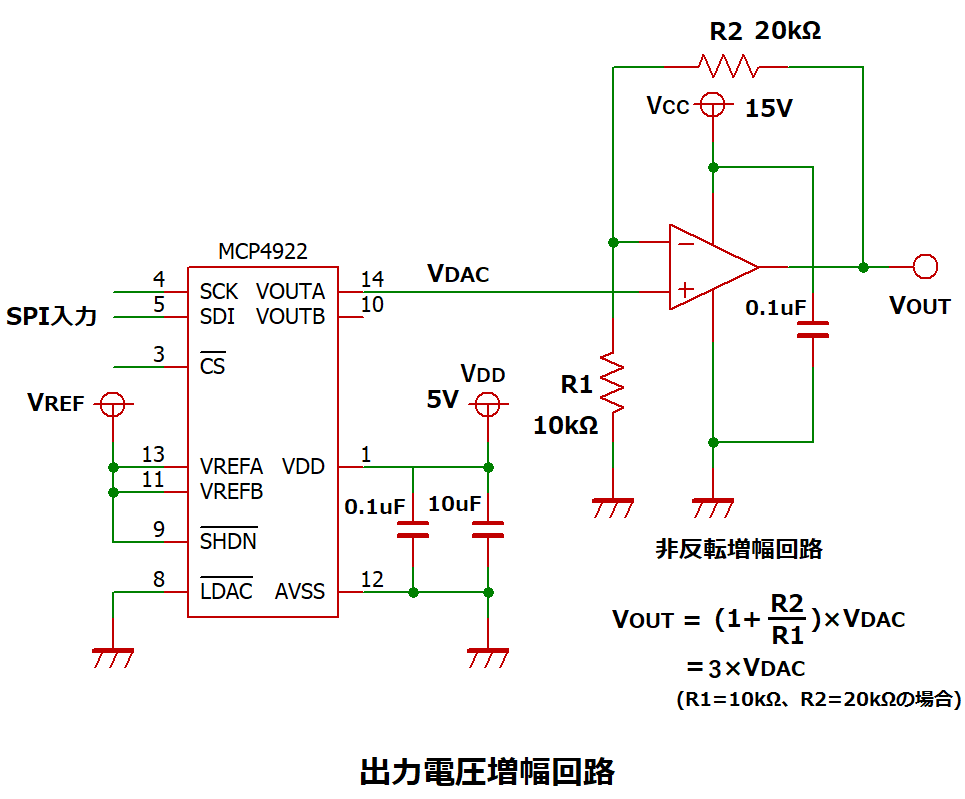

回路例1:出力電圧増幅回路

DACの出力電圧VDACは電源電圧VDDより高くできませんが、

非反転増幅回路と組み合わせることで、出力電圧VOUTを増幅させて出力できます。

(オペアンプの電源電圧VCCはVOUTより高い電圧である必要があります)

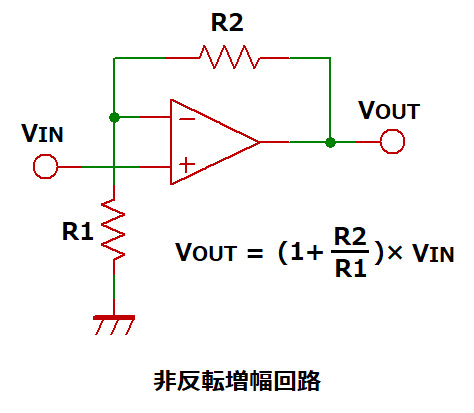

非反転増幅回路の出力電圧の式は以下になります。

上式になる理由については、下記で解説しています。

VINにDACの出力VDACを接続すると、

VOUT=(1+R2/R1)×VDAC・・・式(1)

R1 = 10 kΩ、R2 = 20 kΩとすると、

VOUT=(1+2)×VDAC=2VDAC

となり、出力電圧を3倍にできます。

但し、VOUTはオペアンプの電源電圧VCCよりも大きくできませんが、

15V電源動作のものを選択すれば、

5Vが上限のDACに対し、3倍の15V付近まで増幅できます。

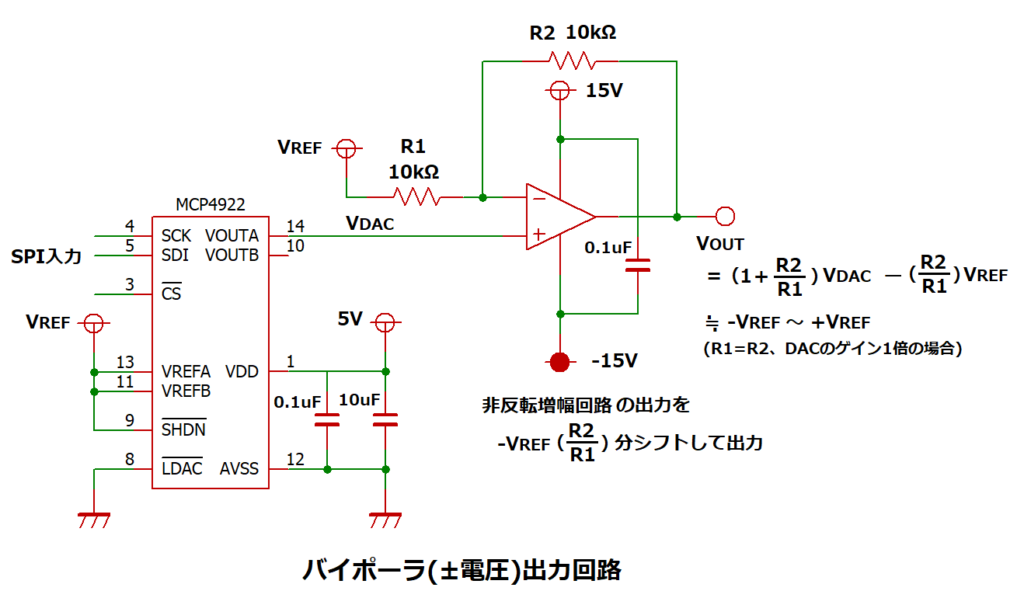

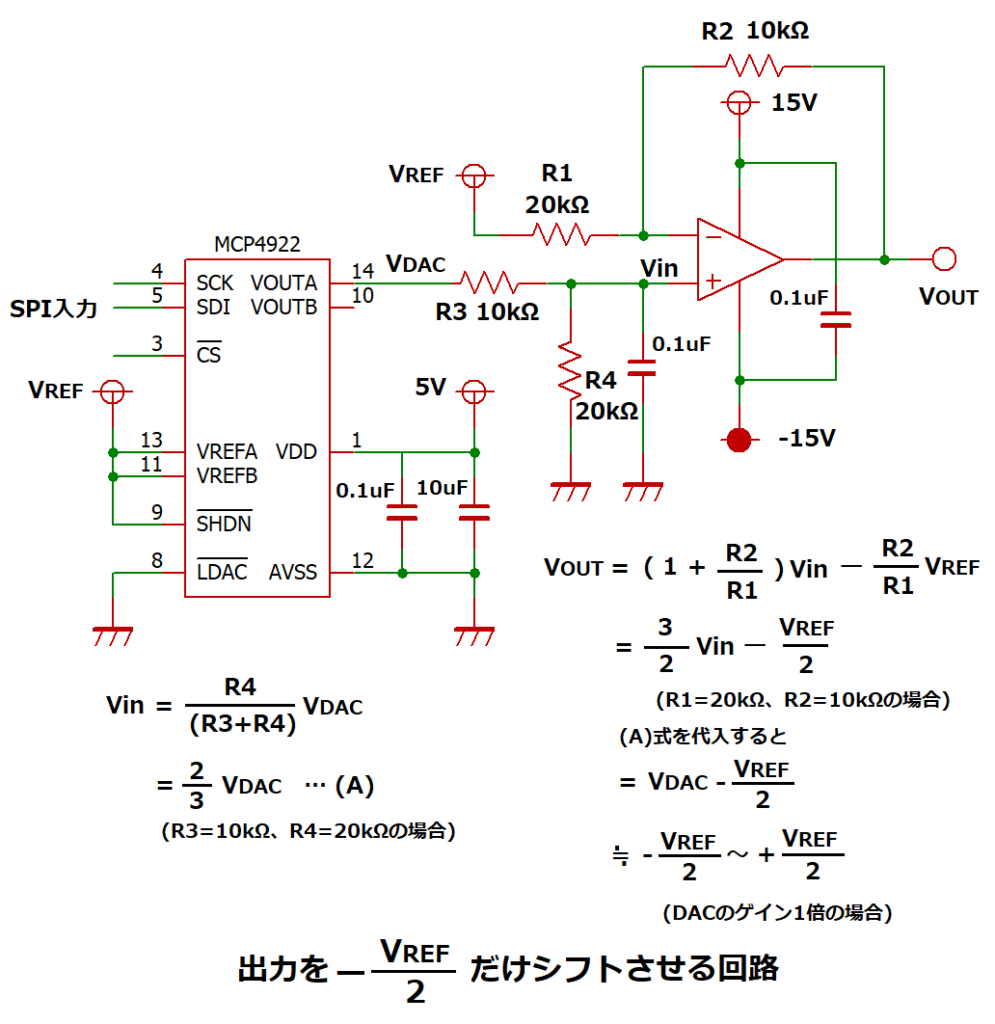

回路例2:バイポーラ(±電圧)出力回路

本DACはユニポーラ(単電圧)出力なので、

そのままでは負電圧は出力できませんが、

回路例1の非反転増幅回路のー端子に電圧を加えて、

出力電圧をー側にシフトさせることで、バイポーラ(±電圧)出力にできます。

但し、オペアンプは負電圧が出力できる両電源タイプにする必要があります。

出力電圧VOUTは以下の式となります。

VOUT=(1+R2/R1)VDACー(R2/R1)VREF・・・(式2)

※式2になる理由は後で説明します。

R1 = 10 kΩ、R2 = 10 kΩとすると、

VOUT=2VDACーVREF

DACのゲインGが1倍の場合、VDACの最大値は

1×4095/4096×VREF≒VREFになるので、

VOUTの最大電圧は、

VOUT(max)≒2VREFーVREF=VREF

DACの最小値0Vの時は、

VOUT(min)≒0ーVREF=ーVREF

となり、

VDAC=0~VREFまで変化した時に、VOUT≒ーVREF~+VREFが出力されます。

これは、VDACの出力を2倍に増幅したことになるので、

1LSBも2倍(2VREF/4096なので、1ビットあたりの電圧変化が2倍)となり、

出力電圧設定が粗くなってしまいます。

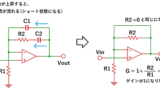

<1LSBを維持したまま±出力にする場合>

出力電圧設定を粗くしたくない場合は、

VDACの出力を増幅せずに、VREFの半分だけ-側にシフトさせることで、

±電圧範囲は半分になりますが、単出力時の1LSBを維持したまま±出力できます。

VDACをR3とR4で抵抗分圧したものを+端子に入力させると、

+端子の電圧Vinは、

Vin=VDAC(R4/(R3+R4))

R1=20 kΩ、R2=10 kΩ、R3=10 kΩ、R4=20 kΩとすると、(式2)より

VOUT=Vin(1+R2/R1)ーVREF(R2/R1)

=VDAC(2/3)((3/2)ーVREF/2

=VDACーVREF/2

先程と同様、DACのゲインGが1倍の場合、VDACの最大値はほぼVREFになるので、

VOUT(max)≒VREFーVREF/2=VREF/2

VDACの最小値は0Vなので、

VOUT(min)≒0ーVREF/2=ーVREF/2

となり、

VDAC=0~VREFまで変化した時に、VOUT≒ーVREF/2~+VREF/2が出力されます。

これは、VDACの出力をVREF/2だけー方向にシフトさせたことになります。

この時の1LSBはVREF/4096となり、単出力時の分解能と同じです。

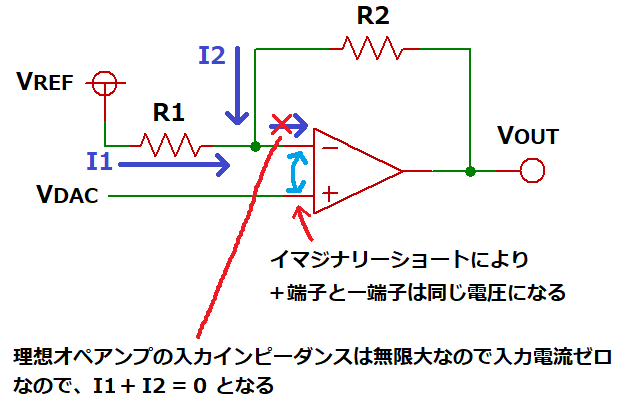

<式2 になる理由>

オペアンプは、出力がー端子に戻る(負帰還)構成の場合、

イマジナリーショート(+と-端子が同電位)になる特性を持つので、

ー端子の電圧はVDACとなります。

この時、この時VREF側から流れる電流I1は

I1=(VREFーVDAC)/R1

VOUT側から流れる電流I2は、

I2=(VOUTーVDAC)/R2

理想的なオペアンプは入力インピーダンスが無限大なので、

ー端子に入力電流は流れないため、I1とI2は相殺されます。

I1+I2=0

従って、

(VREFーVDAC)/R1+(VOUTーVDAC)/R2=0

式を変形すると、

VOUT=(1+R2/R1)VDACー(R2/R1)VREF

となり、式2になります。

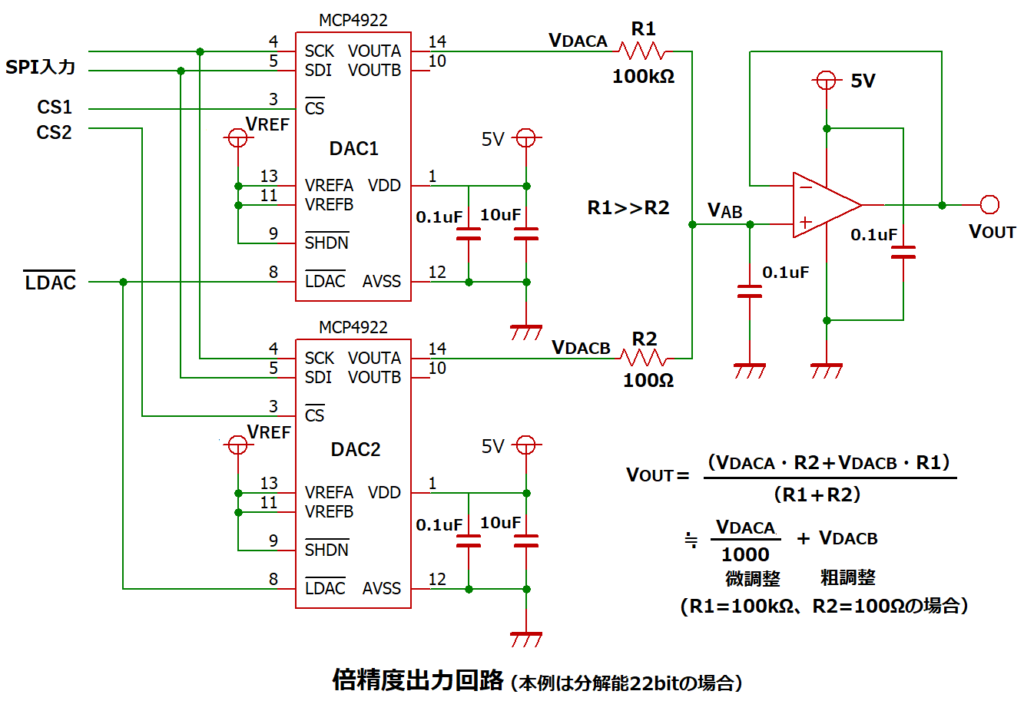

回路例3:倍精度DAC

DAC を2個用いて、分解能を2倍(24bit)まで上げることができます。

出力電圧VOUTは以下の式となります。

VOUT=(VDACA・R2+VDACB・R1)/(R1+R2)・・・(式3)

※式3になる理由は後で説明します。

ここでR1はR2より十分大きな値(R1>>R2)にする必要があります。

例えば、R1 = 100 kΩ、R2 = 100Ωの場合、

式3の分母となるR1+R2は、ほぼ100kΩなので、

VOUT≒VDACA/1000+VDACB

となり、VDACBは、そのままの電圧がVOUTに反映されますが、

VDACAは1/1000にされた電圧が加わります。

この時、VREF=2.048V 、ゲイン2倍にすると、VDACB側の分解能は

1LSB=2×2.048/4096=0.001V=1mV

VDACAは1/1000 になるので、VDACA側の分解能は

1mV/1000=1uVとなります。

以上の動作により、DAC1で微調整、DAC2で粗調整を行うことで、

細かい電圧設定が可能になります。

また、LADC入力を共通化し、両DACを同じタイミングで出力させることで、

式3で示すVOUT電圧を出力できます。

本例の場合、12bit分解能(212=4096)を1000分割(210=1024)したので、

12+10=22bitの分解能を持つDACになりましたが、

抵抗値の組合せにより最大24bitの分解能を持たせることが可能です。

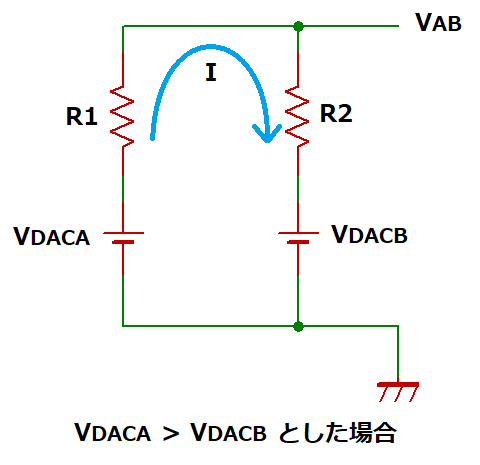

<式3になる理由>

この回路の最終段はゲイン1倍のボルテージフォロワなので、

VOUT=VAB

となります。

2個のDACの出力を合成した電圧VABですが、

各DACの出力電圧VDACA、VDACBをそれぞれ電源と考えると、

以下の回路に置き換えて考えることができます。

ここで、仮にVDACA>VDACBとした時に

VDACAからVDACBへ流れる電流をIとすると、

I=(VDACAーVDACB)/(R1+R2)

R1の電圧降下は

R1×I=R1×(VDACAーVADCB)/(R1+R2)

なので、VABは以下の式で表すことができます。

VAB=VDACAーR1×I

=VDACAーR1×(VDACAーVDACB)/(R1+R2)

=(VDACA×R2+VDACB×R1)/(R1+R2)

となり式3になります。

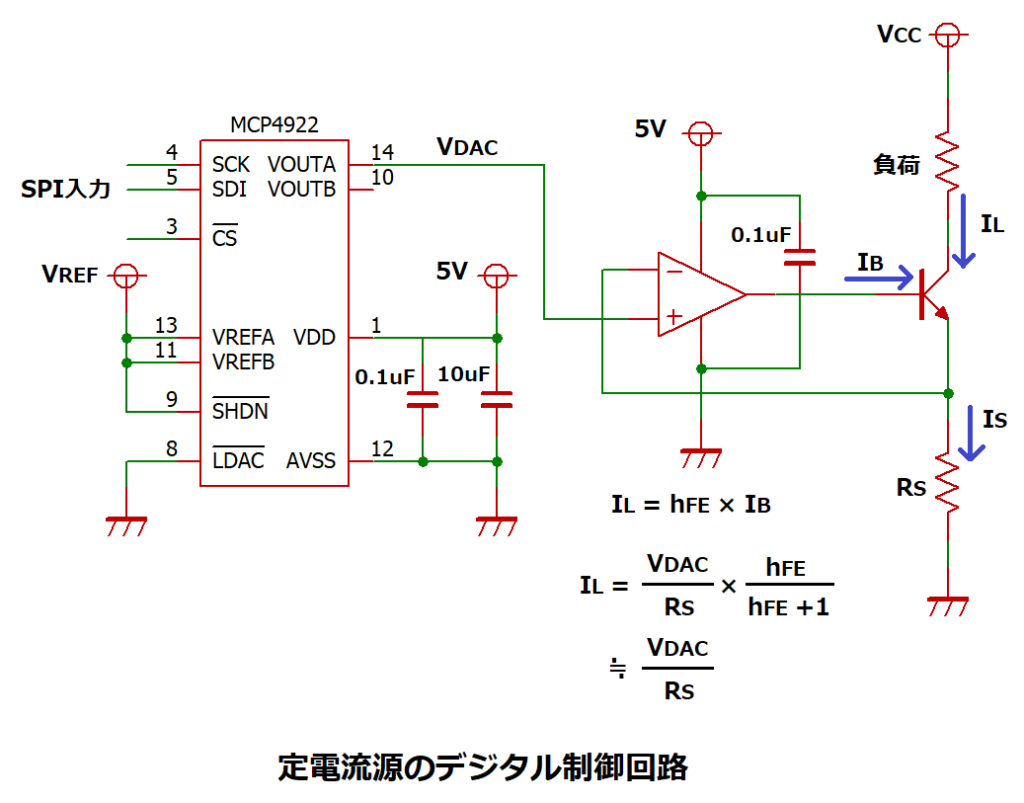

回路例4:定電流源のデジタル制御回路

オペアンプとトランジスタを使用した定電流源回路の電流値設定をDACで行う回路です。

負荷に流れる定電流ILは以下の式となります。

IL=VDAC/RS×hFE/(hFE+1) ・・・(式4)

hFEはトランジスタの電流増幅率です。

一般的なトランジスタのhFEは100程度なので、

IL=VDAC/RS×100/101

=VDAC/RS×0.99

≒VDAC/RS

となり、負荷電流ILは、DACの出力電圧を検出抵抗RSで割った値になるので、

デジタル制御可能な定電流源を構成できます。

RSが小さいほど、RSでの消費電力は少なくできますが、

その分、VDACも低電圧になるため、分解能が低下します。

分解能を高くするためには、VREFを下げるか、

VDACを抵抗分圧する等の対策が必要です。

<式4になる理由>

「式2になる理由」で述べた

オペアンプのイマジナリーショート(+と-端子は同電位になる)により、

RSの電圧をVRとした場合、

VDAC=VR

となります。

RSに流れる電流をISとすると、

IS=VR/RS=VDAC/RS ・・・①

ISは負荷電流ILとトランジスタのベース電流Ibの合計になるので、

IS=IL+Ib ・・・②

トランジスタの電流増幅率がhFEの場合

IL=hFE×Ib ・・・③

①②③を合成すると以下の式になります。

IS=VDAC/RS =IL+Ib=IL+IL/hFE

これを変形すると

VDAC/RS =IL(1+1/hFE)

IL=VDAC/RS ×hFE/(hFE+1)

となり、式4になります。

★オペアンプにつける並列コンデンサの意味について解説してます。

★トランジスタやFETの設計方法についてのまとめ記事です。

★半田付けのコツや部品の外し方を解説しています。